# H24/3688

####

#### Sec. Research Graduate School Committee

11111

Under the Copyright Act 1968, this thesis must be used only under the normal conditions of scholarly fair dealing for the purposes of research, criticism or review. In particular no results or conclusions should be extracted from it, nor should it be copied or closely paraphrased in whole or in part without the written consent of the author. Proper written acknowledgement should be made for any assistance obtained from this thesis.

### Errata

p 7 para 5, line 2: "[6]" for "[5]"

p 159 section title 7.3.2: "Metal-Oxide Varistor (MOV)" for "Varistor (MOV)"

p 186 para 2: Comment: The nominal low voltage line to line value is 415 V in Australia

p 212 figure caption 9.19(b): "Supply" for "LSupply"

p 212 figure 9.19: Replace entire caption with:

" Test 1 - Experimental (a) load current, and (b) active filter and source current waveforms."

p 262 para 2, line 3: "aging" for "ageing"

# DESIGN AND CONTROL OF A UNIVERSAL CUSTOM POWER CONDITIONER (UCPC)

A thesis submitted in accordance with the regulations of Monash University in fulfillment of the requirements for the degree of Doctor of Philosophy

by

Michael John Newman

BSc, Monash University, 1998 BE(Hons), Monash University, 2000

Department of Electrical and Computer Systems Engineering Monash University Victoria, Australia

September 2003

Dedicated to my parents, Lorraine and Adrian

# Contents

| Tə | ble c  | of Contents                                                               | i |

|----|--------|---------------------------------------------------------------------------|---|

| Li | st of  | Figures vii                                                               | i |

| Li | st of  | Tables xvi                                                                | i |

| Al | bstra  | ct xi                                                                     | ĸ |

| De | eclara | ation xx                                                                  | i |

| A  | cknov  | vledgements xxii                                                          | i |

| ₽ı | ıblica | ations                                                                    | V |

| G! | lossat | ry of Terms xxvi                                                          | i |

| Li | st of  | Symbols Used xxi:                                                         | ĸ |

| 1  | Intr   | oduction                                                                  | 1 |

|    | 1.1    | Background                                                                | 1 |

|    | 1.2    | Aim of the Research                                                       | 3 |

|    | 1.3    | Research Approach                                                         | 3 |

|    | 1.4    | Identification of Original Contribution                                   | 6 |

| 2  | Bac    | kground Review                                                            | 9 |

|    | 2.1    | Power Quality: The Problem                                                | Q |

|    |        | 2.1.1 Terminology and Classification                                      | 0 |

|    | 2.2    | Custom Power: Power Electronic Solutions                                  | 4 |

|    |        | 2.2.1 Voltage Source Inverters (VSI) and Current Source Inverters (CSI) 1 | 4 |

|    |        | 2.2.2 Custom Power Topologies                                             | 6 |

- in

•

Color Suite

•.

. .†

.+

|   |     | 2.2.3    | Active Filters (AF)                               | 20 |

|---|-----|----------|---------------------------------------------------|----|

|   |     | 2.2.4    | Uninterruptible Power Supplies (UPS)              | 21 |

|   |     | 2.2.5    | Dynamic Voltage Restorers (DVR)                   | 21 |

|   |     | 2.2.6    | Combined Series-Shunt Topologies                  | 23 |

|   |     | 2.2.7    | Practical Implementation of Custom Power Systems  | 27 |

|   | 2.3 | Summ     | ary                                               | 28 |

| 3 | The | Unive    | ersal Custom Power Conditioner (UCPC)             | 29 |

|   | 3.1 | Overal   | Il Objectives of the UCPC                         | 30 |

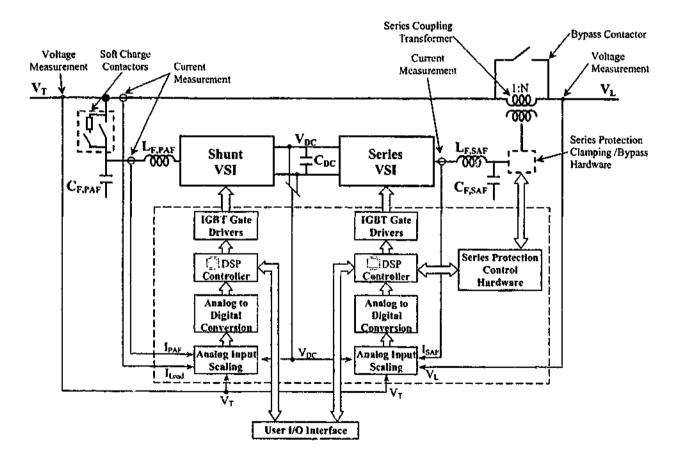

|   | 3.2 | Physic   | cal Components of the UCPC                        | 32 |

|   |     | 3.2.1    | Primary Power Components                          | 33 |

|   |     | 3.2.2    | Ancillary Power Components                        | 33 |

|   |     | 3.2.3    | Analog Measurement Hardware                       | 34 |

|   |     | 3.2.4    | Controller Hardware                               | 34 |

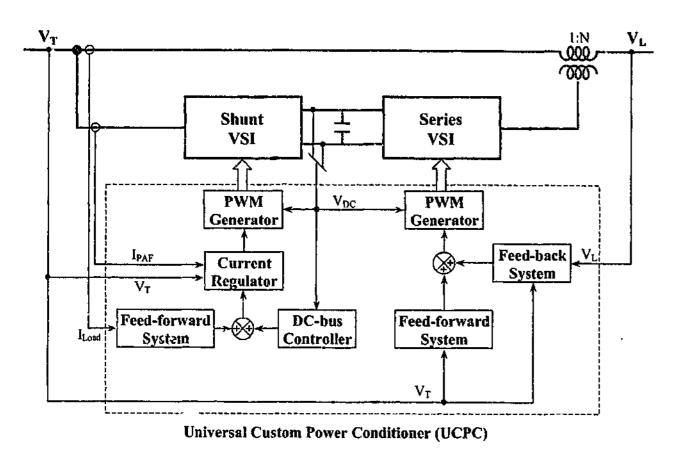

|   | 3.3 | Contro   | ol Concepts for the UCPC                          | 35 |

|   |     | 3.3.1    | Voltage Regulation of the Series Converter        | 36 |

|   |     | 3.3.2    | Current Regulation of the Shunt Converter         | 37 |

|   |     | 3.3.3    | Combined Series-Shunt Operation of the UCPC       | 38 |

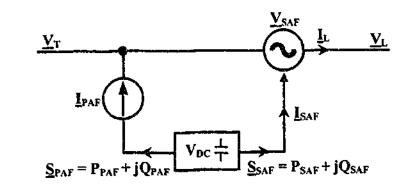

|   | 3.4 | Rating   | gs and Injection Capabilities of the UCPC         | 39 |

|   |     | 3.4.1    | UCPC Sag Injection                                | 40 |

|   |     | 3.4.2    | UCPC Steady-State Power Flow                      | 40 |

|   |     | 3.4.3    | Series Voltage Injection Requirements             | 42 |

|   |     | 3.4.4    | Shunt Current Injection Requirements              | 42 |

|   |     | 3.4.5    | Equating Energy Flow Constraints                  | 44 |

|   |     | 3.4.6    | Compatibility Limits for UCPC Protected Equipment | 45 |

|   |     | 3.4.7    | Series-Shunt Orientation Options                  | 47 |

|   | 3.5 | Netwo    | ork Placement of the UCPC                         | 48 |

|   | 3.6 | Summ     | ary                                               | 53 |

| 4 | Con | ntrol of | f the UCPC System                                 | 55 |

|   | 4.1 | UCPC     | C System Analysis                                 | 56 |

|   | 4.2 | Series   | Voltage Injection Control System Overview         | 57 |

|   |     | 4.2.1    | Supply Voltage Feed-forward                       | 57 |

|   |     | 4.2.2    | Load Voltage Selective Feed-back                  | 59 |

|   |     |          |                                                   |    |

## ii

|   |      | 4.2.3   | Design and Stability Analysis                                  | 61         |

|---|------|---------|----------------------------------------------------------------|------------|

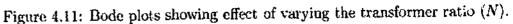

|   | 4.3  | Shunt   | Current Injection Control System Overview                      | 71         |

|   |      | 4.3.1   | Reference Signal Creation                                      | 72         |

|   |      | 4.3.2   | Predictive Current Regulation (PCR)                            | 73         |

|   | 4.4  | Summ    | ary                                                            | 76         |

| 5 | Stat | tionary | y Reference Frame Control                                      | 77         |

|   | 5.1  | Statio  | nary Frame Linear Controllers                                  | 78         |

|   |      | 5.1.1   | P+Resonant Controllers                                         | 79         |

|   |      | 5.1.2   | P+Resonant Selective Harmonic Compensation                     | 82         |

|   | 5.2  | Paran   | neter Design of the Stationary Frame Series Controller         | 87         |

|   |      | 5.2.1   | Effect of the Feed-forward Component                           | 88         |

|   |      | 5.2.2   | Design of $K_I$                                                | <b>9</b> 0 |

|   |      | 5.2.3   | Design of $K_P$                                                | 92         |

|   |      | 5.2.4   | Design of $f_C$                                                | 94         |

|   |      | 5.2.5   | Active Damping Feed-back                                       | 94         |

|   |      | 5.2.6   | Series Controller Design Process                               | 99         |

|   |      | 5.2.7   | Final System Parameter Values                                  | 101        |

|   | 5.3  | Statio  | nary Frame Shunt Current Reference Extraction                  | 104        |

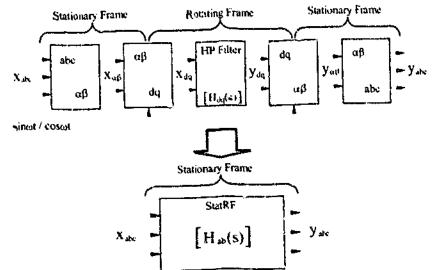

|   |      | 5.3.1   | Reference Signal Extraction Overview                           | 105        |

|   |      | 5.3.2   | Proposed Stationary Reference Frame (StatRF) Signal Extraction | 106        |

|   |      | 5.3.3   | Practical StatRF Fixed-Point DSP Implementations               | 114        |

|   | 5.4  | Summ    | ary                                                            | 118        |

| 6 | Dig  | ital Co | ontrol: The Delta Operator                                     | 119        |

|   | 6.1  | Digita  | l Control in Custom Power Applications                         | 120        |

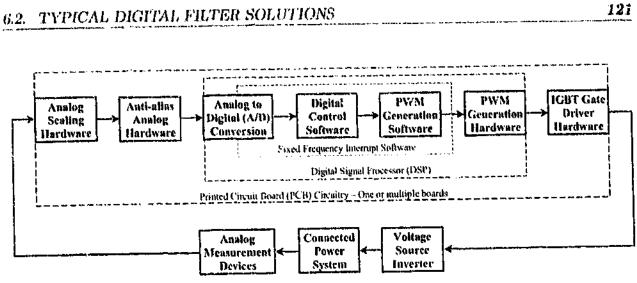

|   | 6.2  | Typica  | al Digital Filter Solutions                                    | 121        |

|   |      | 6.2.1   | Shift operator based Infinite Impulse Response (IIR) Filters   | 122        |

|   |      | 6.2.2   | Finite Impulse Response (FIR) Filters                          | 126        |

|   |      | 6.2.3   | Alternative Filtering Techniques                               | 131        |

|   | 6.3  | The D   | Delta Operator                                                 | 133        |

|   |      | 6.3.1   | Delta operator based IIR Digital Filtering                     | 135        |

|   |      | 6.3.2   | Choice of $\Delta$ ,                                           | 136        |

|   |      | 6.3.3   | Direct Form Structures                                         | 137        |

iii

100

τĒ.

|   | 6.4 | Fixed-point Implementation                                                  | I |

|---|-----|-----------------------------------------------------------------------------|---|

|   |     | 6.4.1 Overflow Minimization and Clamping Techniques                         | ł |

|   |     | 6.4.2 Internal Truncation Compensation                                      | ł |

|   |     | 6.4.3 Coefficient Rounding                                                  | ł |

|   |     | 6.4.4 Integer Scaling and $\Delta$ Selection                                |   |

|   | 6.5 | Delta IIR versus Shift IIR                                                  | ; |

|   |     | 6.5.1 Example 1: StatRF Harmonic Reference Generator                        | i |

|   |     | 6.5.2 Example 2: P+Resonant Controller                                      | • |

|   | 6.6 | Summary                                                                     | • |

| 7 | Con | trol of UCPC Protection System 153                                          | i |

|   | 7.1 | Shunt converter Protection                                                  | Ł |

|   | 7.2 | Series converter Protection                                                 | ŀ |

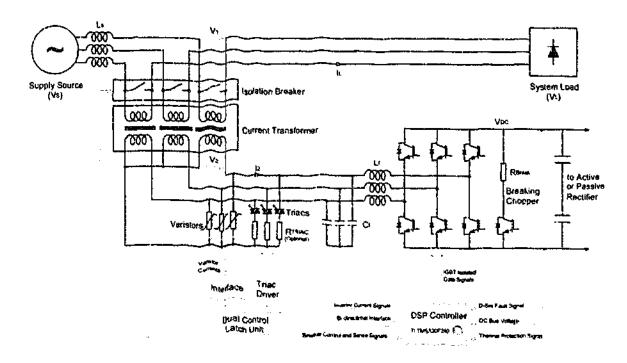

|   |     | 7.2.1 Introduction to Protection Issues for Series Injection Converters 154 | ŧ |

|   |     | 7.2.2 Previous Literature                                                   | į |

|   |     | 7.2.3 Overview of the proposed Integrated Series Protection Scheme 157      | • |

|   | 7.3 | Elements of the Integrated Series Protection System                         | 1 |

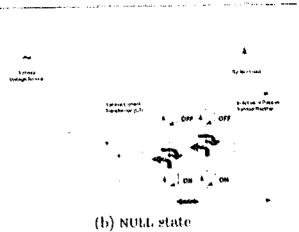

|   |     | 7.3.1 Insulated Gate Bipolar Transistor (IGBT) NULL State                   | 1 |

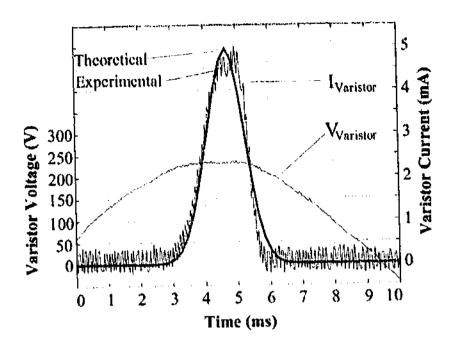

|   |     | 7.3.2 Varistor (MOV)                                                        | ) |

|   |     | 7.3.3 Thyristors/Triacs and Series Resistors                                | ; |

|   |     | 7.3.4 Primary Breaker                                                       | 6 |

|   |     | 7.3.5 DC Bus "Braking" Chopper                                              | Ł |

|   |     | 7.3.6 Transformer Design                                                    | ŧ |

|   | 7.4 | Series Protection System Operation                                          | Ł |

|   | 7.5 | Simulation and Experimental Verification                                    | i |

|   | 7.6 | Summary                                                                     |   |

| 8 | Sim | ulation Verification 173                                                    | ; |

|   | 8.1 | Continuous Series Model Simulations                                         | Ł |

|   | 8.2 | Digital Controller Frequency Sweep Simulations                              | i |

|   | 8.3 | Complete UCPC Detailed Simulation                                           | 5 |

|   | 8.4 | UCPC Simulation Results                                                     | ł |

|   | 8.5 | Summary                                                                     | 2 |

| 9  | Low  | Volta  | ge Experimental Verification                             | 185  |

|----|------|--------|----------------------------------------------------------|------|

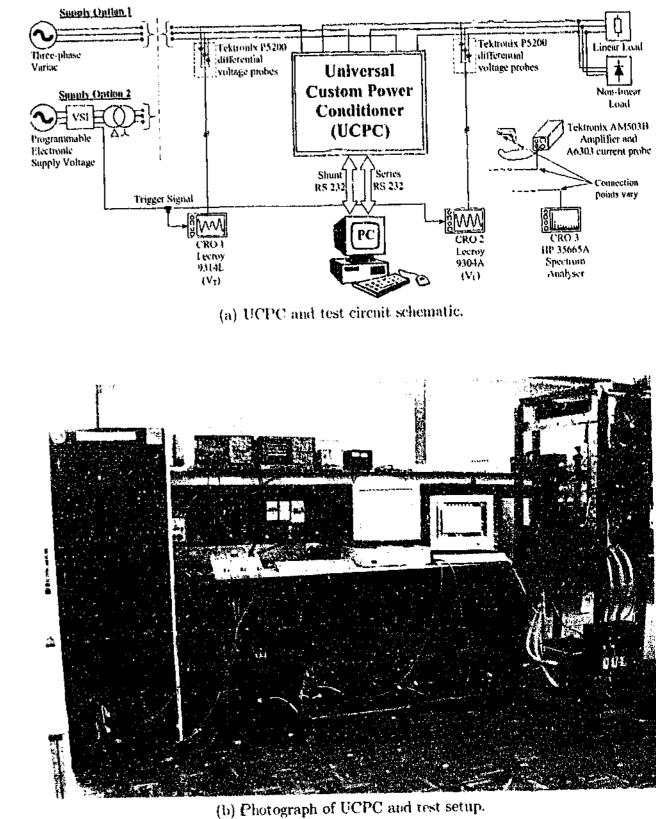

|    | 9.1  | Experi | mental System Overview                                   | 186  |

|    | 9.2  | Hardw  | are Development and Configuration                        | 187  |

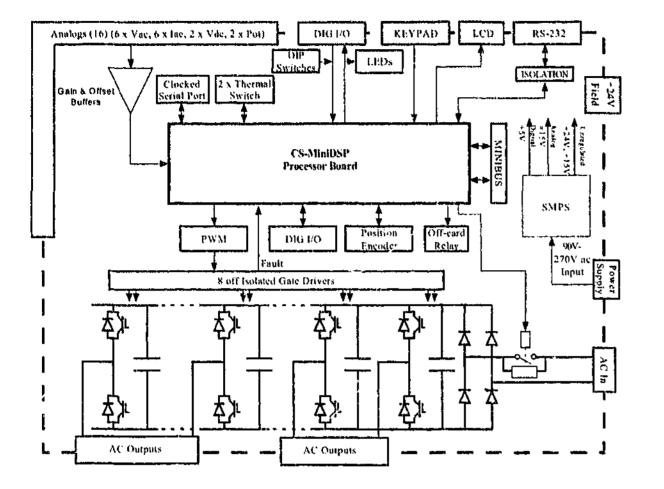

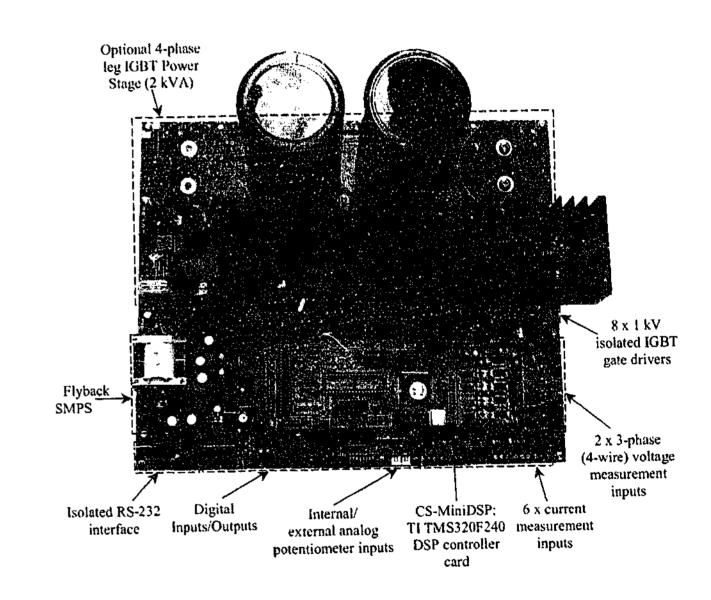

|    |      | 9.2.1  | Controller Hardware - Integrated Inverter Board (CS-IIB) | 187  |

|    |      | 9.2.2  | Voltage Source Inverters (VSI)                           | 192  |

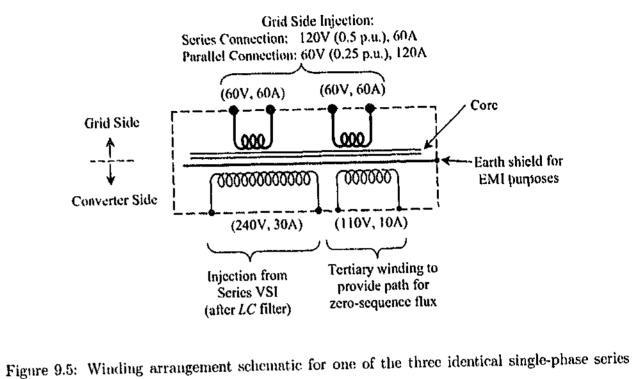

|    |      | 9.2.3  | Series Injection Transformers                            | 193  |

|    |      | 9.2.4  | Protection Components                                    | 196  |

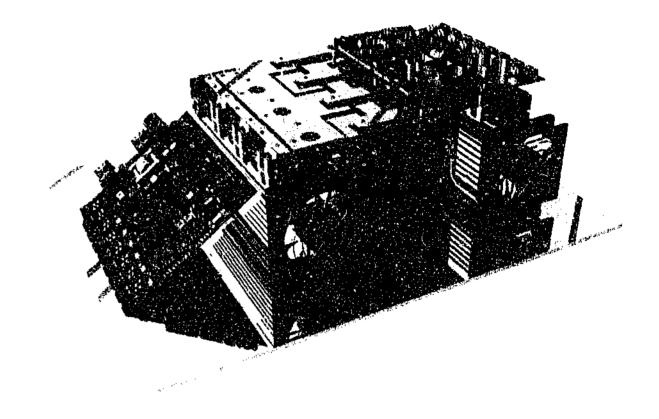

|    |      | 9.2.5  | Housing and Construction                                 | 196  |

|    | 9.3  | DSP S  | oftwar^ Systems                                          | 199  |

|    |      | 9.3.1  | Bar. ground Software                                     | 199  |

|    |      | 9.3.2  | Interrupt Software                                       | 199  |

|    | 9.4  | Test S | ctup and Measurement                                     | 202  |

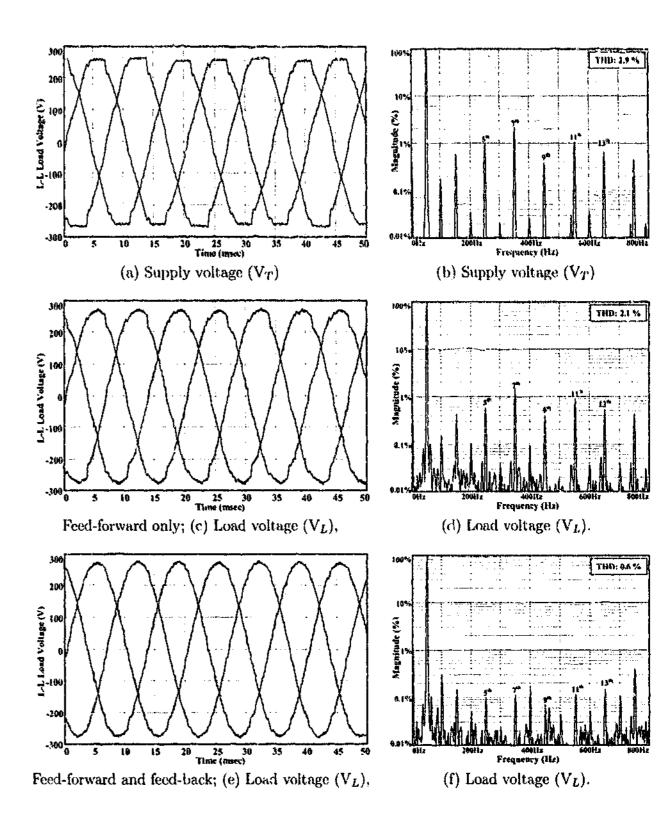

|    | 9.5  | Experi | imental Results                                          | 204  |

|    |      | 9.5.1  | Steady State Voltage Compensation                        | 204  |

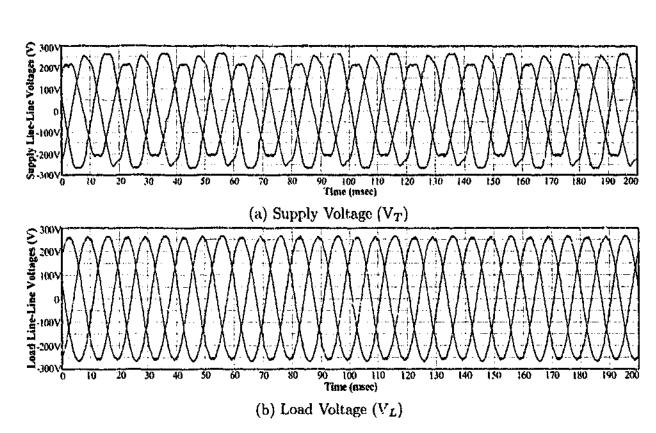

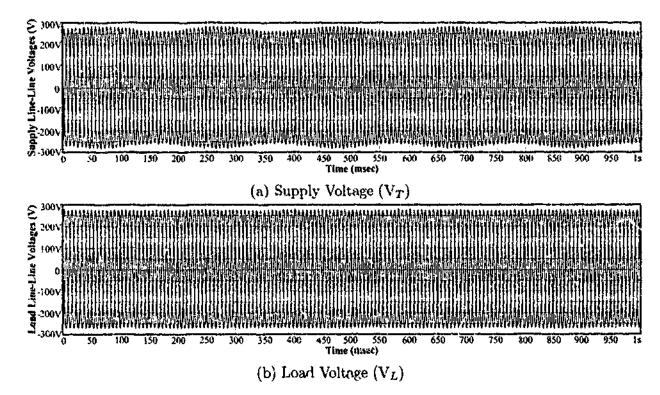

|    |      | 9.5.2  | Transient Voltage Compensation                           | 208  |

|    |      | 9.5.3  | Current Compensation                                     | 212  |

|    | 9.6  | Summ   | ary                                                      | 215  |

| 10 | 34   | 12 ٦   | Alter The suit out 1 Marife astice                       | 0177 |

| ιυ |      |        | Voltage Experimental Verification                        | 217  |

|    |      |        | iew and Objectives                                       |      |

|    | 10.2 |        | m Voltage DVR Prototype                                  |      |

|    |      |        | DVR System Overview                                      |      |

|    |      |        | Medium Voltage Test Grid                                 |      |

|    |      |        | Measurement Systems                                      |      |

|    |      |        | Controller Hardware and DVR Control Software             |      |

|    |      | 10.2.5 | Initial DVR Experimental Results                         | 223  |

|    | 10.3 | DVR v  | with Voltage Harmonic Compensation                       | 225  |

|    |      | 10.3.1 | Proposed Additional Selective Voltage Harmonic Control   | 226  |

|    |      | 10.3.2 | Start-up Tests                                           | 229  |

|    |      | 10.3.3 | Steady-State Harmonic Compensation Tests                 | 229  |

|    |      | 10.3.4 | Dynamic Sag and Harmonic Compensation Tests              | 238  |

|    | 10.4 | Summ   | ary                                                      | 241  |

v

| ĺ | 3 | 0 | ٨ | 11 | E | V | 7 | S |

|---|---|---|---|----|---|---|---|---|

|---|---|---|---|----|---|---|---|---|

| 11 | Con         | clusion                                                 | 243         |

|----|-------------|---------------------------------------------------------|-------------|

|    | 11.1        | Summary of the Work                                     | 244         |

|    |             | 11.1.1 The Universal Custom Power Conditioner (UCPC)    | 244         |

|    |             | 11.1.2 Stationary Frame Signal Extraction               | 245         |

|    |             | 11.1.3 Digital Implementation                           | 245         |

|    |             | 11.1.4 Protection                                       | <b>2</b> 46 |

|    |             | 11.1.5 Experimental Verification Processes              | 246         |

|    | 11.2        | Suggestions for Future Work                             | 247         |

|    |             | 11.2.1 Multi-level Implementations                      | 247         |

|    |             | 11.2.2 Further Experimental and Control Investigations  | 247         |

|    |             | 11.2.3 UCPC Network Application Research                | 248         |

|    |             | 11.2.4 Effects of PWM on Closed-loop Linear Controllers | 248         |

|    | 11.3        | Closure                                                 | 249         |

| A  | Pow         | er Quality                                              | 251         |

|    |             | Power Quality and the Consumer                          |             |

|    | A.2         | Terminology and Classification                          |             |

|    |             | Power Quality Standards                                 |             |

|    | A.4         |                                                         |             |

|    |             | A.4.1 Equipment Susceptibility                          |             |

|    |             | A.4.2 Event Probability                                 | 256         |

|    |             | A.4.3 Equipment Compatibility                           | 257         |

|    | A.5         | Voltage Unbalance (Type 4)                              | 259         |

|    |             | Waveform Distortion (Type 5)                            |             |

|    |             | Voltage Fluctuations - Flicker (Type 6)                 |             |

|    | A.8         | Summary                                                 | 261         |

| Ð  | S;          | es Parameter Values                                     | 263         |

| D  | B.1         |                                                         |             |

|    |             | Final LV Experimental Parameters                        |             |

|    | 1,2         |                                                         | 404         |

| С  | Mat         | thematical Working                                      | 267         |

|    | <b>C</b> .1 | Four-Wire StatRF using Exact Transformation             | 267         |

|    | C.2         | Three-Wire StatRF using Exact Transformation            | 269         |

|    | <b>C.3</b>  | Single-Phase StatRF using Approximate Transformation    | 270         |

.

vi

| D | Seri | es DSP Software                            | 27       | /1 |

|---|------|--------------------------------------------|----------|----|

|   | D.1  | pwmint.e: C Interrupt Code                 | <b>2</b> | 71 |

|   | D.2  | pwmback.c: C Background Code               | 29       | 93 |

|   | D.3  | filters.asm: Assembler Digital Filter Code | 3        | 12 |

| E | Shu  | ut DSP Software                            | 32       | 23 |

|   | E.1  | pcrint.c: C Interrupt Code                 | 3:       | 23 |

|   | E.2  | pwmback.c: C Background Code               | 34       | 49 |

|   | E.3  | filters.asm: Assembler Digital Filter Code | 33       | 73 |

# List of Figures

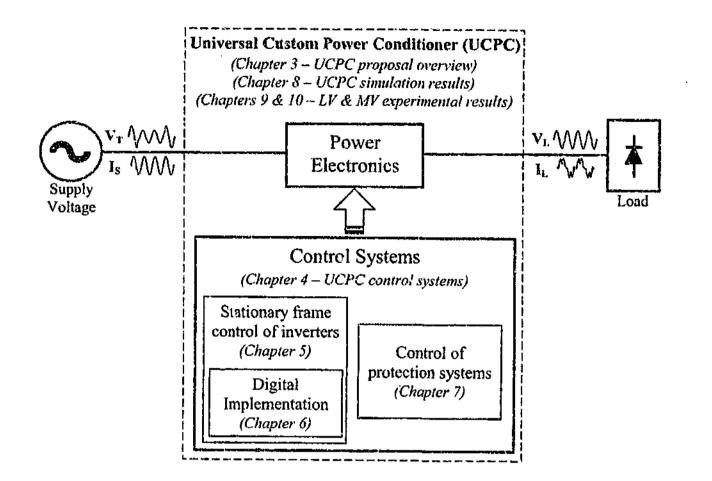

- 1.1 Thesis structure in relation to the

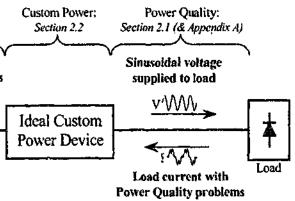

- 2.1 Power Quality compensation examples

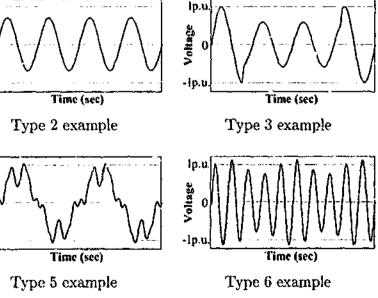

- 2.2 Example waveforms of type 2 to

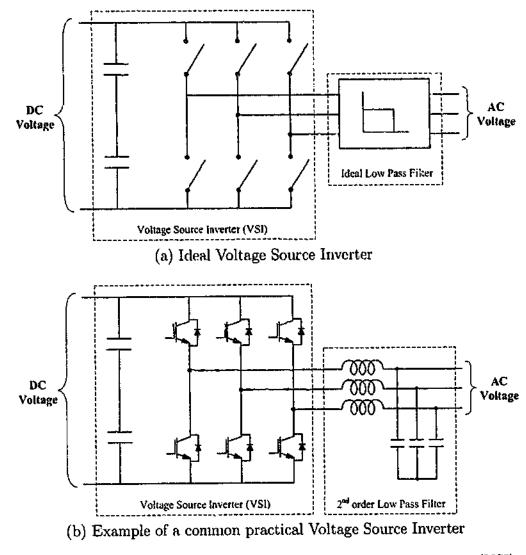

- 2.3 Schematics of ideal and practical

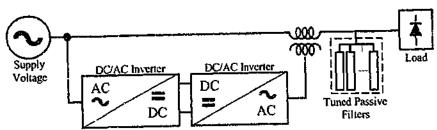

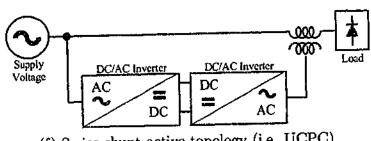

- 2.4 Fundamental Custom Power topo

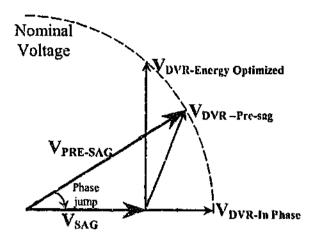

- 2.5 DVR control strategy options phecompensation, and Energy optimi

- 3.1 Overview of the operation and pl tioner (UCPC) in a radial distribu

- 3.2 Physical components of the Unive

- 3.3 General structure of the control sc

- 3.4 Simplified UCPC circuit diagram injection capabilities investigation

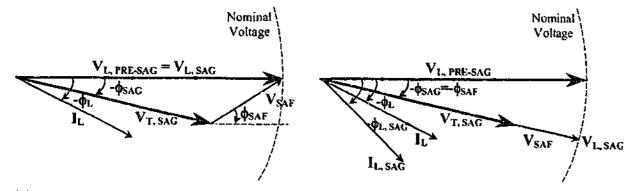

- 3.5 Phasor diagrams for compensation

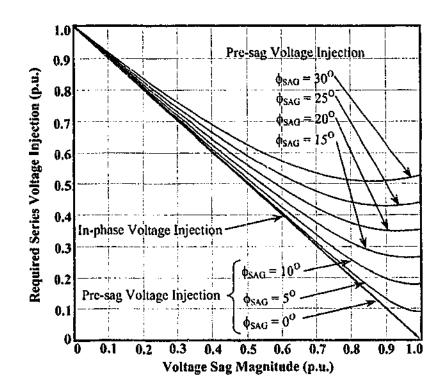

- ? Required series voltage injection of varying depth and phase jump).

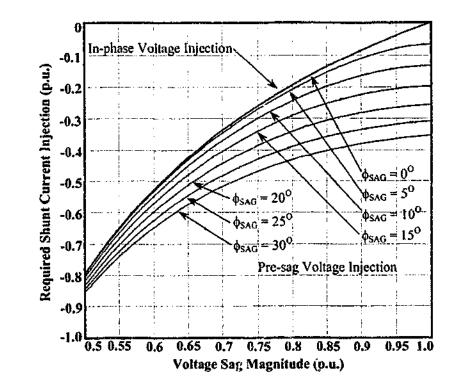

- 3.7 Required shunt currnet injection varying depth and phase jump), v

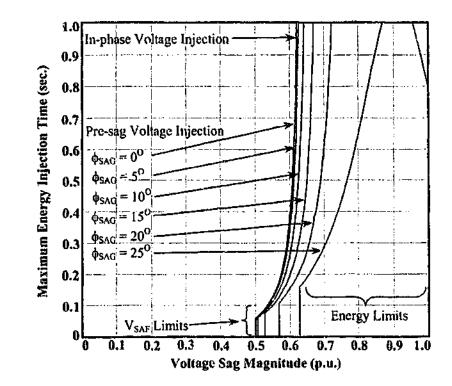

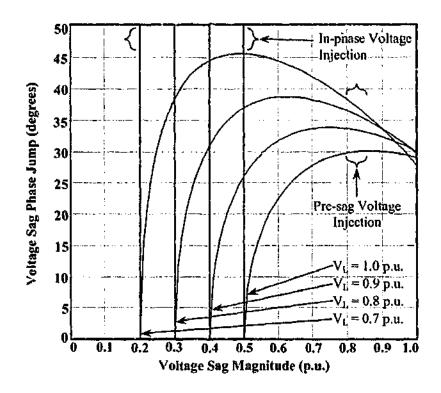

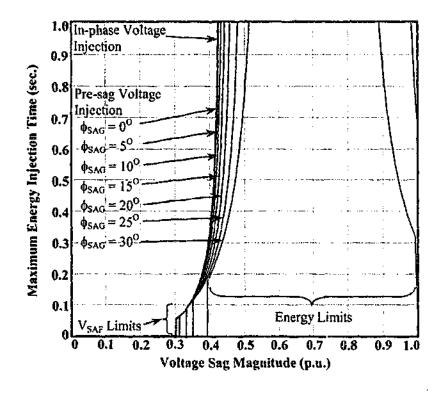

- 3.8 Maximum sag compensation cap  $(t_{SAG})$ , sag depth  $(V_{T,SAG})$  and voltage and a 0.8 p.u. load current

- 3.9 Maximum sag compensation capability injection) with respect to sag dept voltage  $(V_L)$  equipment susceptibility of the second sec

| e Universal Custom Power Conditioner (UCPC).          | 4  |

|-------------------------------------------------------|----|

| mple for an ideal Custom Power device                 | 9  |

| type 6 Power Quality problems                         | 11 |

| Voltage Source Inverters (VSI)                        | 15 |

| ologies                                               | 17 |

| asor diagram: Pre-sag compensation, In-phase          |    |

| ized control. (Adapted from [58])                     | 22 |

| lacement of a Universal Custom Power Condi-           |    |

| ution system.                                         | 31 |

| ersal Custom Power Conditioner (UCPC)                 | 32 |

| cheme of the Universal Custom Power Conditioner.      | 36 |

| n outlining terminology and polarities used for       |    |

| 1                                                     | 39 |

| on of voltage sags using Pre-sag and In-phase         |    |

|                                                       | 40 |

| of the UCPC during voltage sag conditions (i.e.       |    |

| · · · · · · · · · · · · · · · · · · ·                 | 43 |

| of the UCPC during voltage sag conditions (i.e.       |    |

| with 0.8 p.u. load current.                           | 43 |

| pabilities of the UCPC with respect to; time          |    |

| phase jump ( $\phi_{SAG}$ ), with a unity target load |    |

| 9ŧ                                                    | 45 |

| bilities of the UCPC (maximum 0.5 p.u. voltage        |    |

| th and phase jump, with varying minimum load          |    |

| ility limits                                          | 46 |

ix

## LIST OF FIGURES

A REAL PROPERTY OF

の見ていたのである

- SIGNATION

a set of the ball and the set

Constant of the

| 3.10 | Maximum sag compensation capabilities of the UCPC with respect to time $(t_{SAG})$ ,           |    |

|------|------------------------------------------------------------------------------------------------|----|

|      | sag depth $(V_{T,SAG})$ and phase jump $(\phi_{SAG})$ , with a target load voltage of 0.8 p.u. |    |

|      | and a 0.8 p.u. load current.                                                                   | 46 |

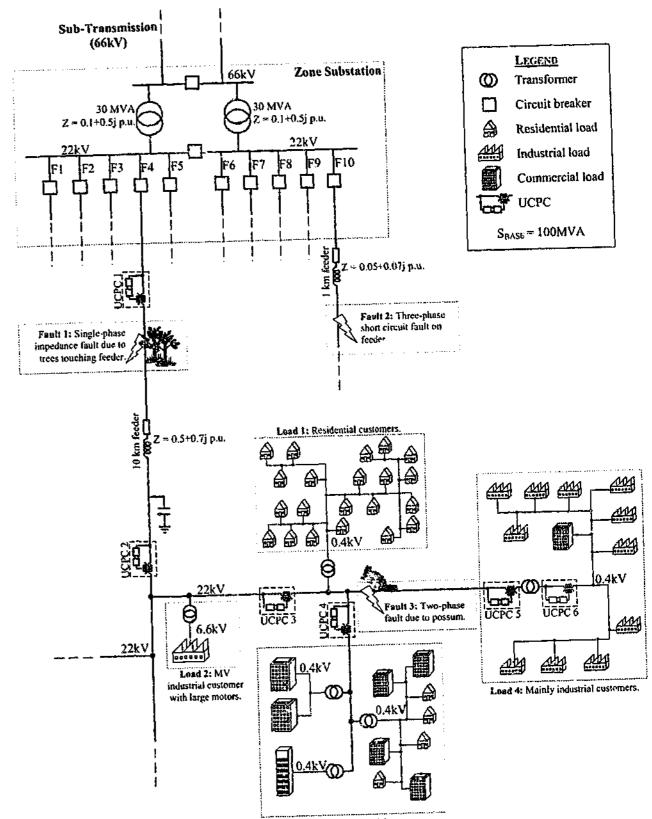

| 3.11 | Flacement options for a UCPC in an example distribution system.                                | 49 |

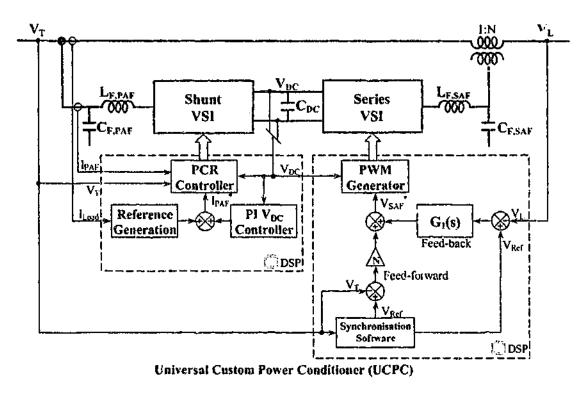

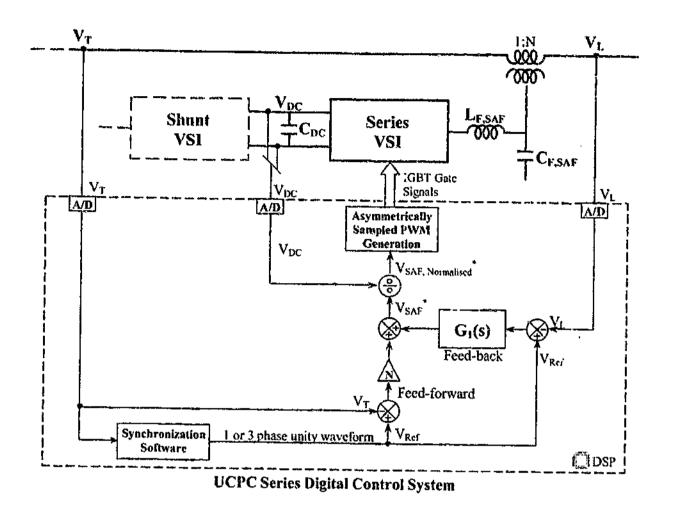

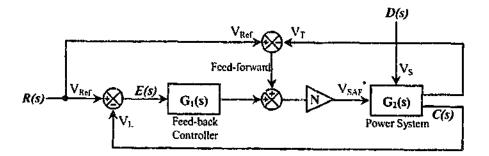

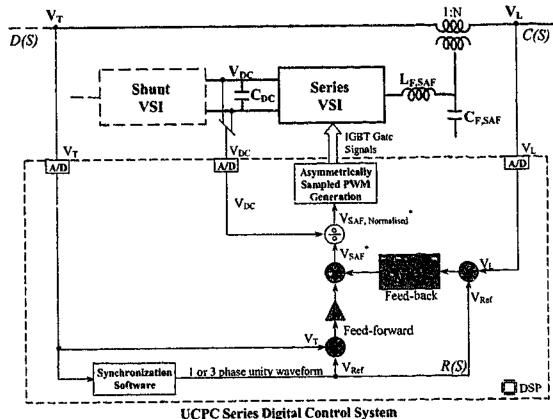

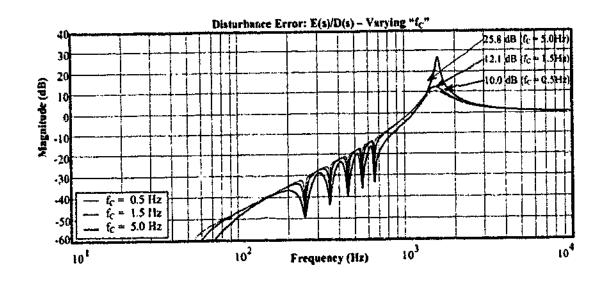

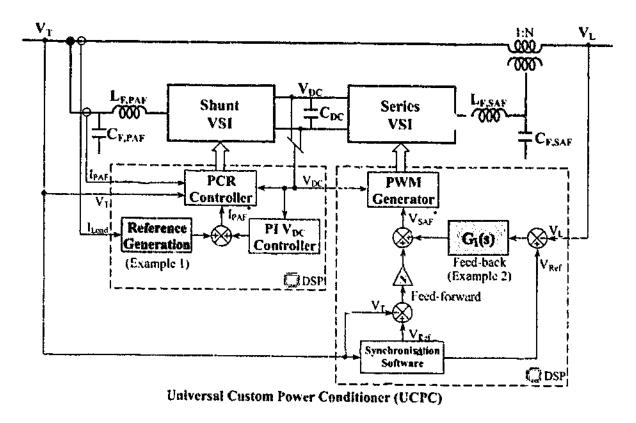

| 4.1  | Proposed control scheme for the Universal Custom Power Conditioner.                            | 56 |

| 4.2  | Components of the series injection control system.                                             | 58 |

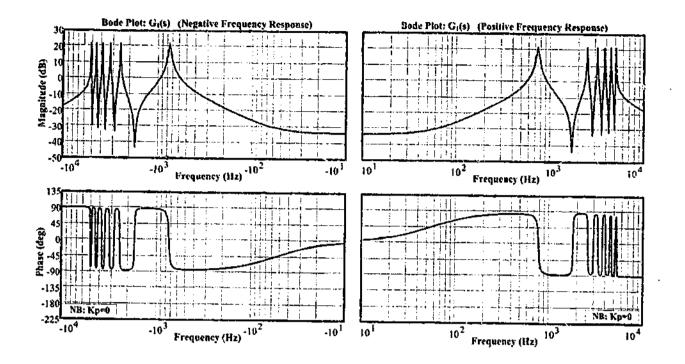

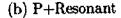

| 4.3  | Simulated positive and negative bode plots for the series feed-back controller,                |    |

|      | $G_1(s)$ . (Proportional gain equals zero)                                                     | 60 |

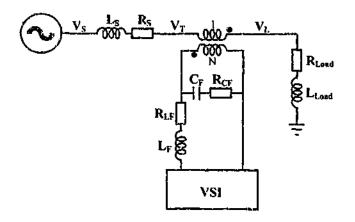

| 4.4  | Electrical elements and labels used for stability analysis of the series control system,       | 62 |

| 4.5  | Control block overview of the series injection control system and model of the                 |    |

|      | power system used for stability analysis.                                                      | 62 |

| 4.6  | Power system model used for stability analysis.                                                | 62 |

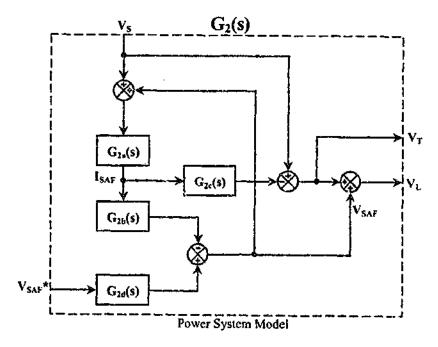

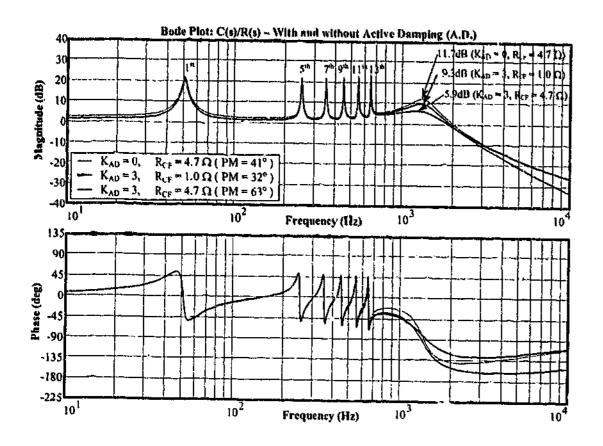

| 4.7  | Bode plots showing effect of varying the filter capacitance $(C_F)$ . (Refer to Table          |    |

|      | B.1 in Appendix B for remaining default parameters.)                                           | 65 |

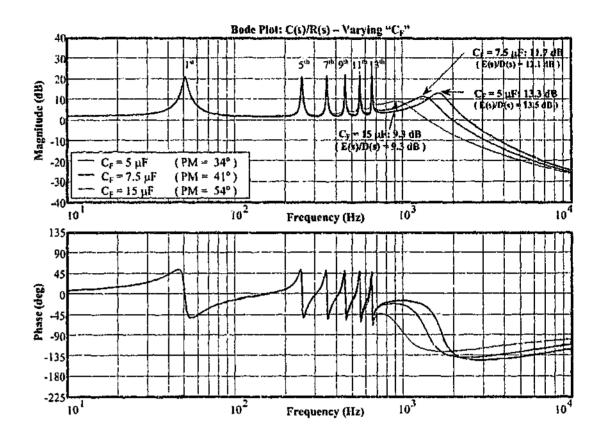

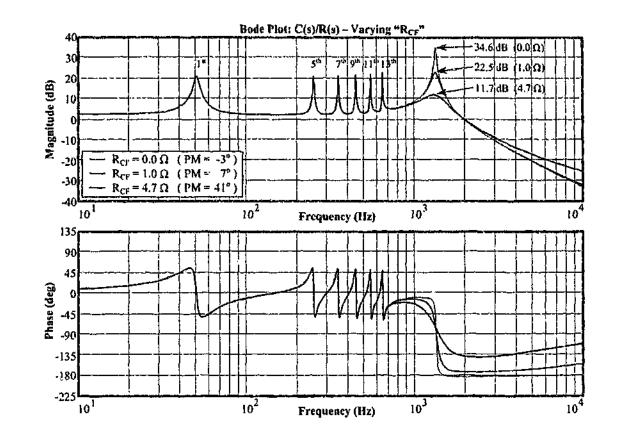

| 4.8  | Bode plots showing effect of varying the filter capacitor series resistance $(R_{CF})$ .       |    |

|      | (Refer to Table B.1 in Appendix B for remaining default parameters.)                           | 67 |

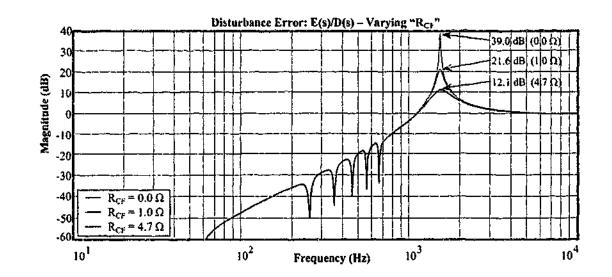

| 4.9  | Disturbance error $E(s)/D(s)$ showing effect of varying the filter capacitor se-               |    |

|      | ries resistance $(R_{CF})$ . (Refer to Table B.1 in Appendix B for remaining default           |    |

|      | parameters.)                                                                                   | 67 |

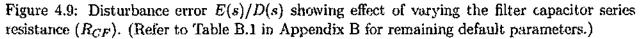

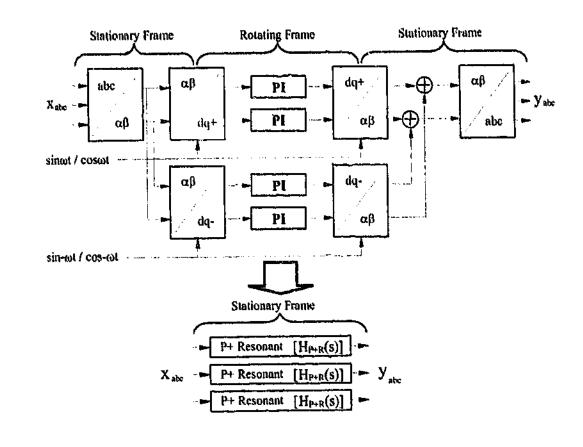

| 4.10 | Bode plots showing effect of varying the load inductance $(L_{Load})$ .                        | 69 |

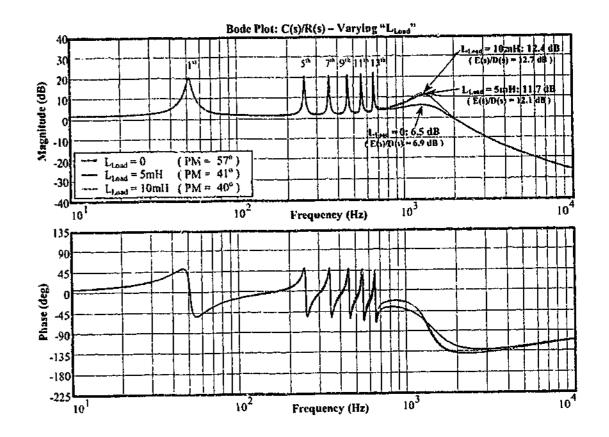

| 4.11 | Bode plots showing effect of varying the transformer ratio $(N)$ .                             | 69 |

| 4.12 | Components of the shunt control system.                                                        | 71 |

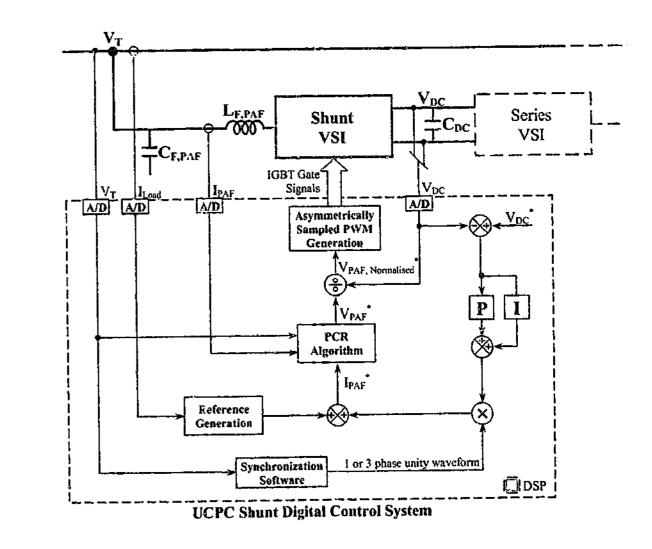

| 4.13 | Current compensation percentage error (per harmonic) caused by a single sample                 |    |

|      | delay in the cancellation current.                                                             | 75 |

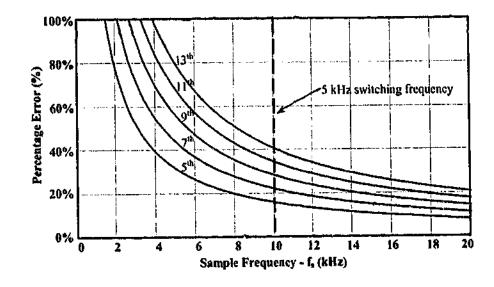

| 5.1  | Conversion of the rotating frame $d$ - $q$ PI controller to the stationary frame P+Resonan     |    |

|      | controllers.                                                                                   | 81 |

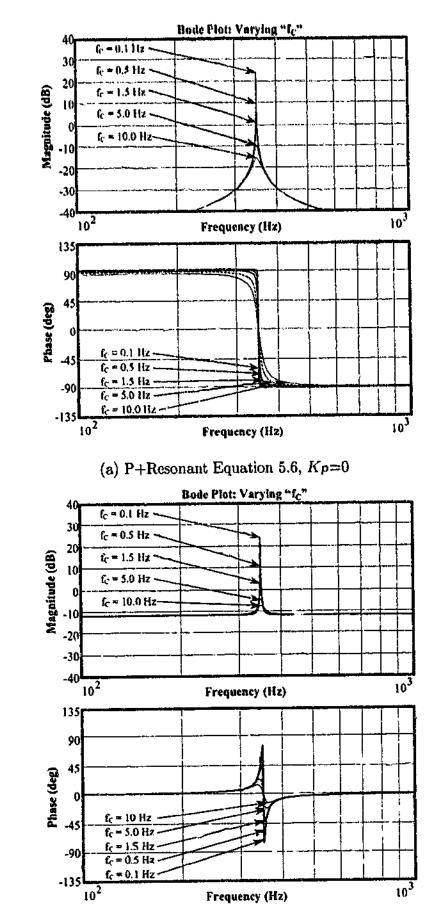

| 5.2  | Simulated open loop frequency response of the P+Resonant controller in Equation                |    |

|      |                                                                                                | 83 |

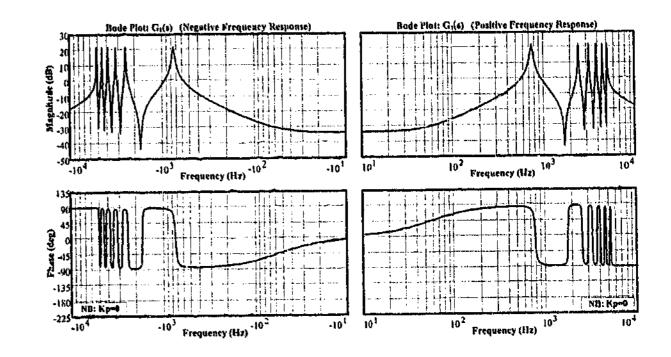

| 5.3  | Simulated open loop frequency response of the P+Resonant in Equation (5.9)                     |    |

|      | controller with varying cut-off frequency.                                                     | 84 |

| 5.4  | Frequency response of the harmonic P+Resonant voltage controllers                              | 85 |

| T O  | F FIGURES                                                                               | xi  |

|------|-----------------------------------------------------------------------------------------|-----|

| 5.5  | Components of the series injection control system. (Stationary frame feed-forward       |     |

|      | and feed-back components highlighted in grey.)                                          | 87  |

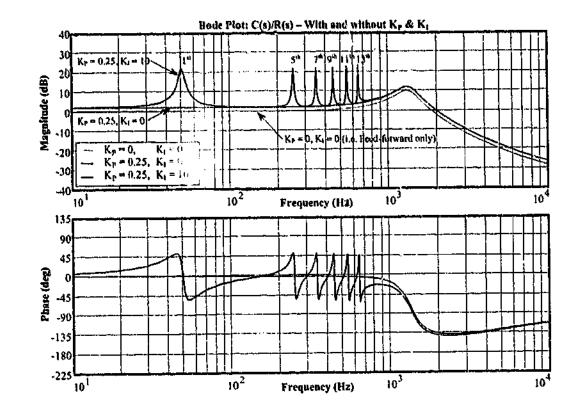

| 5.6  | Bode plots showing effect with and without the integral gain $(K_I)$ , and the pro-     |     |

|      | portional gain $(K_P)$ .                                                                | 89  |

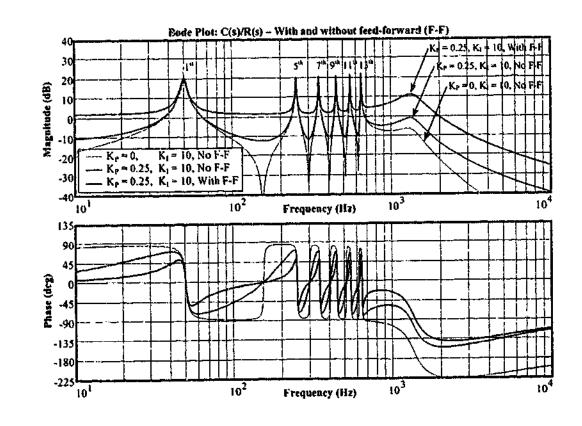

| 5.7  | Bode plots showing effect with and without the feed-forward (F-F) controller            | 89  |

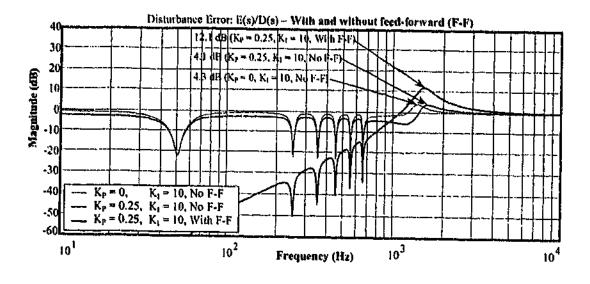

| 5.8  | Disturbance error $E(s)/D(s)$ showing effect of with and without the feed-forward       |     |

|      | (F-F) controller. (Refer to Table B.1 in Appendix B for remaining default pa-           |     |

|      | rameters.)                                                                              | 90  |

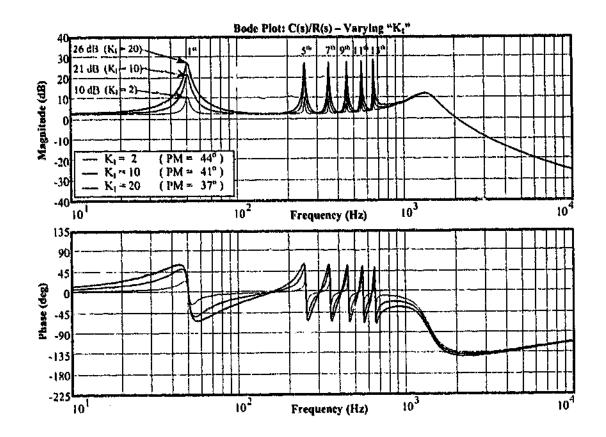

| 5.9  | Bode plots showing effect of varying the integral gain $(K_I)$ . (Refer to Table B.1    |     |

|      | in Appendix B for remaining default parameters.)                                        | 91  |

| 5.10 | Disturbance error $E(s)/D(s)$ showing effect of varying the integral gain $(K_I)$ .     |     |

|      | (Refer to Table B.1 in Appendix B for remaining default parameters.)                    | 91  |

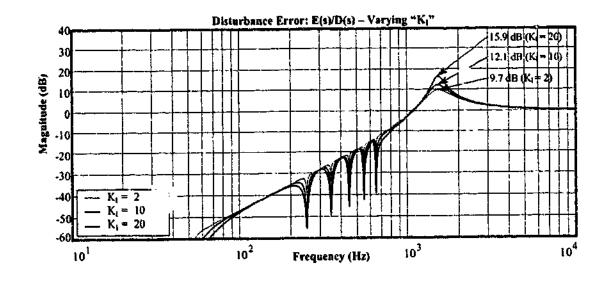

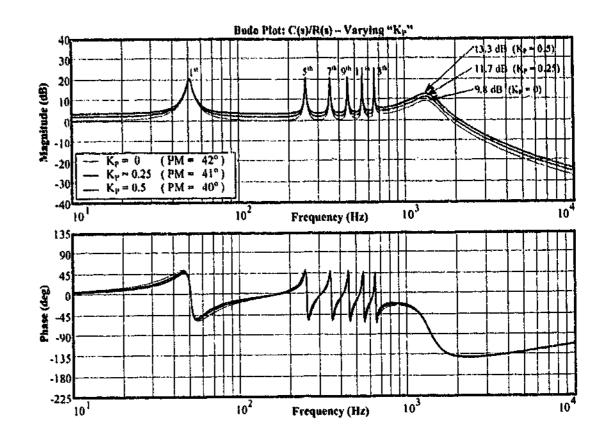

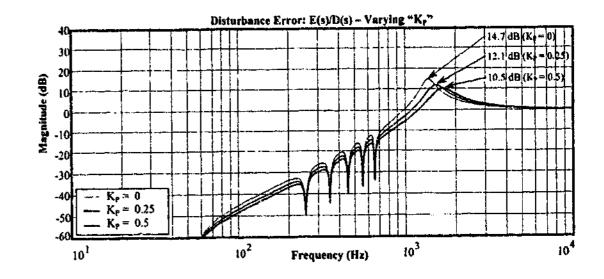

| 5.11 | Bode plots showing effect of varying the proportional gain $(K_P)$ . (Refer to Table    |     |

|      | B.1 in Appendix B for remaining default parameters.)                                    | 93  |

| 5.12 | Disturbance error $E(s)/D(s)$ showing effect of varying the proportional gain           |     |

|      | $(K_P)$ . (Refer to Table B.1 in Appendix B for remaining default parameters.)          | 93  |

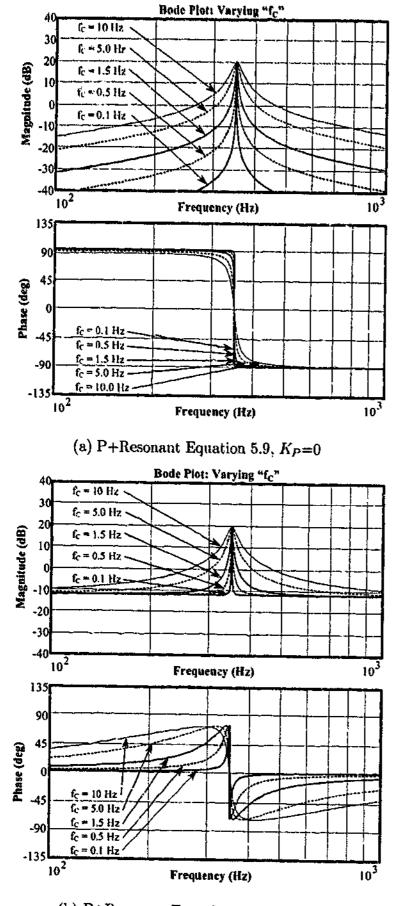

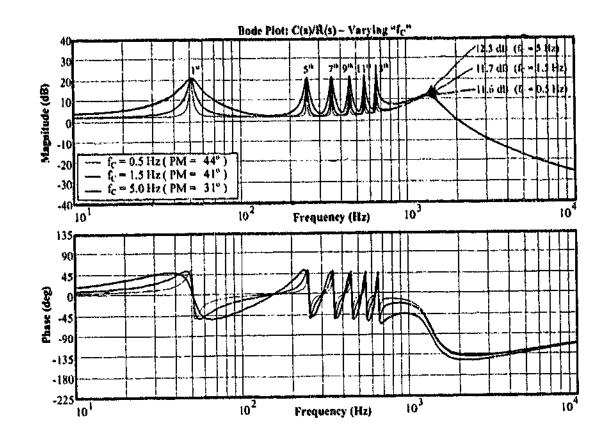

| 5.13 | Bode plots showing effect of varying the cut-off frequency $(f_C)$ . (Refer to Table    |     |

|      | B.1 in Appendix B for remaining default parameters.)                                    | 98  |

| 5.14 | Disturbance error $E(s)/D(s)$ showing effect of varying the cut-off frequency $(f_C)$ . |     |

|      | (Refer to Table B.1 in Appendix B for remaining default parameters.)                    | 98  |

| 5.15 | Components of the series injection control system. (active damping component            |     |

|      | highlighted in grey.)                                                                   | 93  |

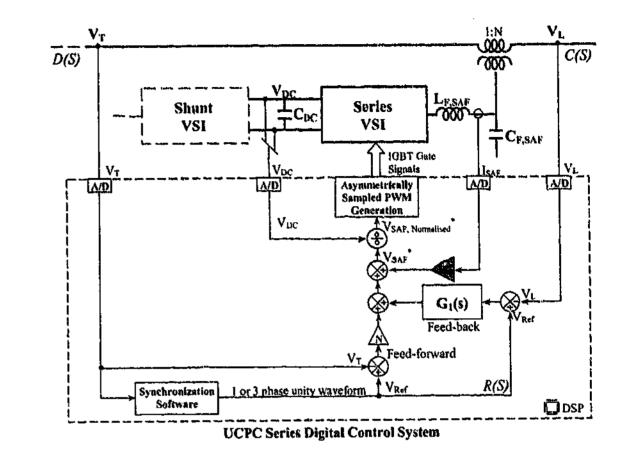

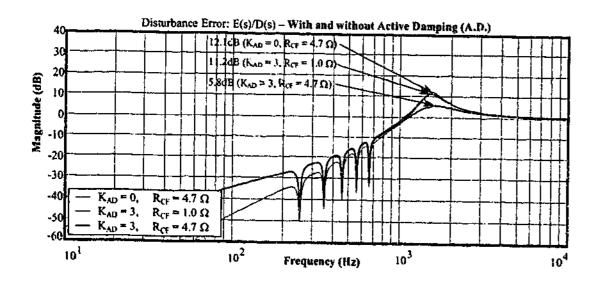

| 5.16 | Bode plots showing effect of the active damping (A.D.) scheme. (Refer to Table          |     |

|      | B.1 in Appendix B for remaining default parameters.)                                    | 98  |

| 5.17 | Disturbance error $E(s)/D(s)$ showing effect of the active damping (A.D.) scheme.       |     |

|      | (Refer to Table B.1 in Appendix B for remaining default parameters.)                    | 98  |

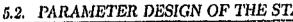

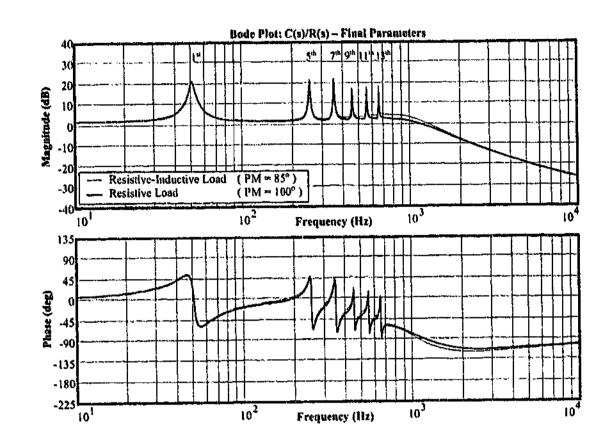

| 5.18 | Bode plots for the final parameters used in the LV experimental work                    | 10  |

| 5.19 | Disturbance error $E(s)/D(s)$ for the final parameters used in the LV experimental      |     |

|      | work                                                                                    | 103 |

| 5.20 | Components of the shunt control system.                                                 | 104 |

| 5.21 | Typical active filter block structure.                                                  | 10  |

| 5.22 | Synchronous Reference Frame (SRF) High Pass (HP) type controller                        | 10  |

| 5.23 | Synchronous Reference Frame (SRF) Low Pass (LP) type controller.                        | 106 |

x

## LIST OF FIGURES

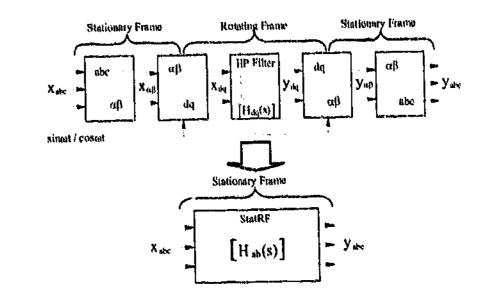

| <b>5.2</b> 4 | Rotating to Stationary Frame conversion of the High Pass (HP) type Synchronous               |

|--------------|----------------------------------------------------------------------------------------------|

|              | Reference Frame (SRF) harmonic extraction unit.                                              |

| 5.25         | Proposed (a) three-wire and (b) four-wire Stationary Reference Frame (StatRF)                |

|              | harmonic extraction units                                                                    |

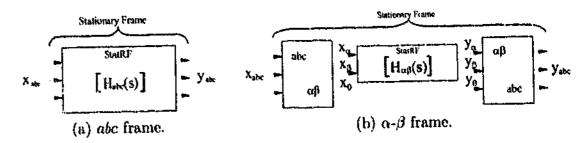

| 5.26         | Comparison of StatRF and SRF frequency characteristics (phase a only): Simulink              |

|              | simulation.                                                                                  |

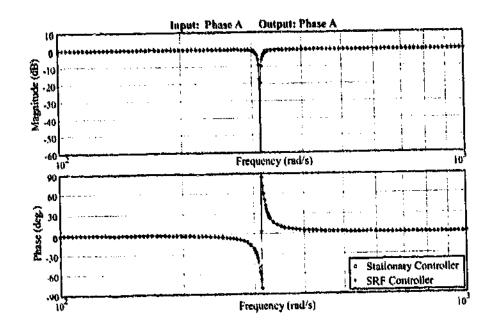

| 5.27         | SRF, StatRF and narrow-band notch comparison.                                                |

|              | Connection of controllers in Matrix $[\mathbf{H}_{ab}(s)]$                                   |

|              | Frequency response for continuous and shift IIR filters with: (a) 20-bit; (b) 16-bit;        |

|              | coefficients                                                                                 |

| 6.1          | Control implementation block diagram for a general Custom Power application                  |

|              | with a single-chip DSP digital controller                                                    |

| 6.2          | Pole clustering effect of a narrowband notch shift-based IIR digital filter (sampling        |

|              | frequency = $2 \text{ kHz} - 10 \text{ kHz}$                                                 |

| 6.3          | Simulations of FIR 16-bit fixed point digital implementations                                |

| 6.4          | Comparison of $11^{th}$ harmonic P+Resonant FIR $h[n]$ coefficients with varying $f_c$ . 130 |

| 6.5          | Comparison of $11^{th}$ harmonic P+Resonant FIR with varying N                               |

| 6.6          | Delta operator construction diagram                                                          |

| 6.7          | Stability regions for the continuous Laplace plane, discrete delta, and discrete             |

|              | shift planes                                                                                 |

| 6.8          | Direct Form (DF) digital filter implementation structures: (a) DFI; (b) DFIt; (c)            |

|              | DFII; (d) DFIIt                                                                              |

| 6.9          | 16-bit fixed-point TI TMS320F240 DSP delta-based IIR software implementation                 |

|              | diagram                                                                                      |

| 6.10         | Delta operator fixed-point DSP software implementation with truncation com-                  |

|              | pensation                                                                                    |

| 6.11         | Truncation and rounding effects from a 16-bit fixed-point DSP                                |

| 6.12         | Proposed control scheme for the Universal Custom Power Conditioner, with con-                |

|              | trollers used for shift/delta comparison examples shown in grey                              |

| 6.13         | Rotating to Stationary Frame conversion of the High Pass (HP) type Synchronous               |

|              | Reference Frame (SRF) harmonic extraction unit                                               |

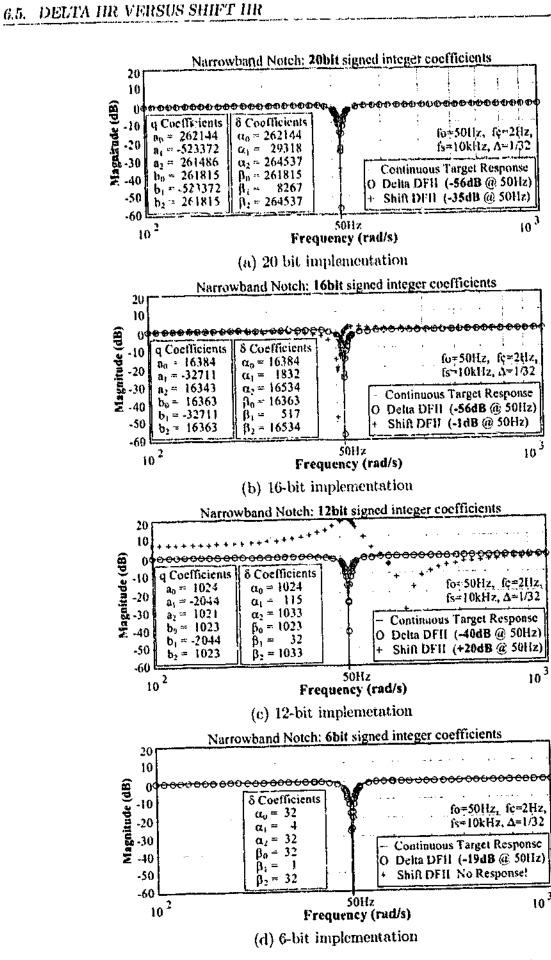

| 6.14         | Frequency response for continuous, shift and delta filters with: (a) 20-bit; (b)             |

|              | 16-bit; (c) 12-bit; (d) 6-bit coefficients                                                   |

## LIST OF FIGURES

「「「「「「「「」」」」「「「「」」」」」「「」」」」」」

いたが、たち、

語言の語言ない

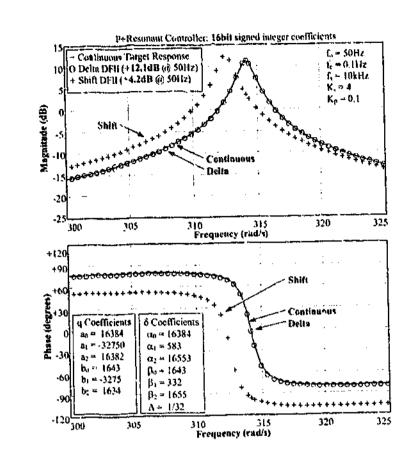

| 6.15 | Open loop frequency response for a  |

|------|-------------------------------------|

|      | filters                             |

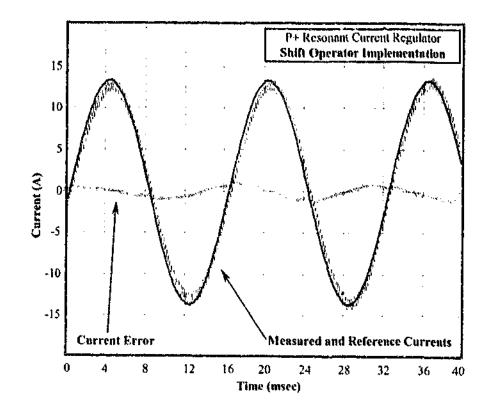

| 6.16 | Experimental results for a shift-ba |

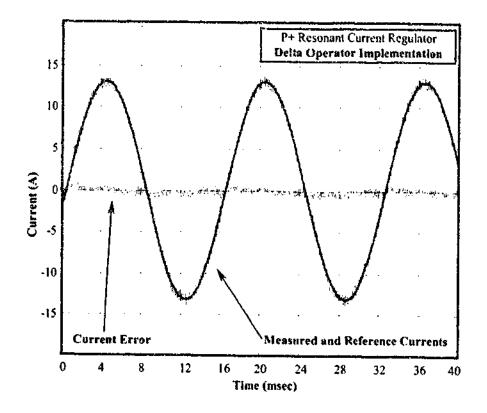

| 6.17 | Experimental results for a delta-b  |

| 6.18 | Simulated open loop frequency re-   |

|      | bit parallel selective P+Resonant   |

|      | controller of the UCPC)             |

| 7.1  | VSI current paths for a series inje |

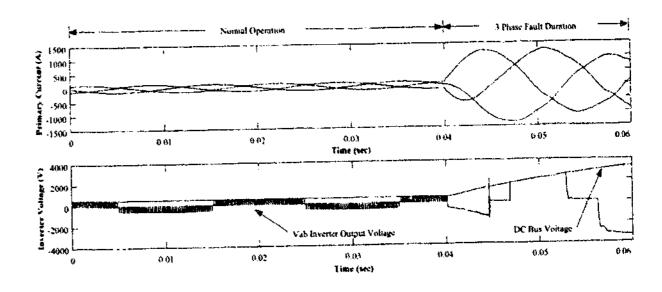

| 7.2  | Fault response of a 250 kVA ser     |

|      | protection system.                  |

| 7.3  | Series injected voltage source inv  |

|      | controllers                         |

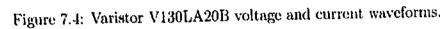

| 7.4  | Varistor V130LA20B voltage and      |

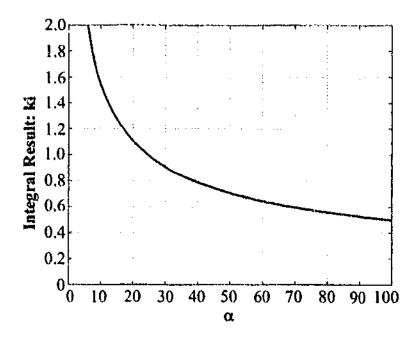

| 7.5  | Numerical integration alpha const   |

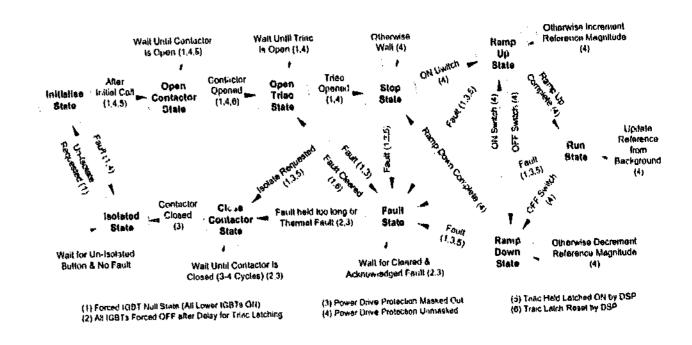

| 7.6  | Series protection and control stat  |

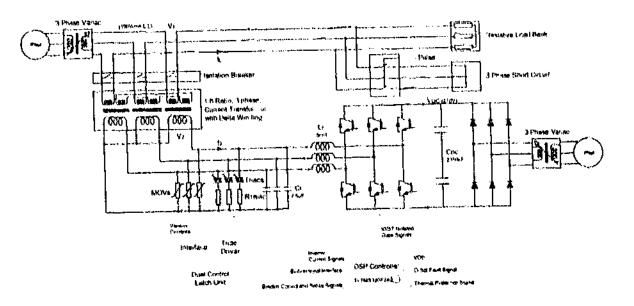

| 7.7  | Experimental series protection an   |

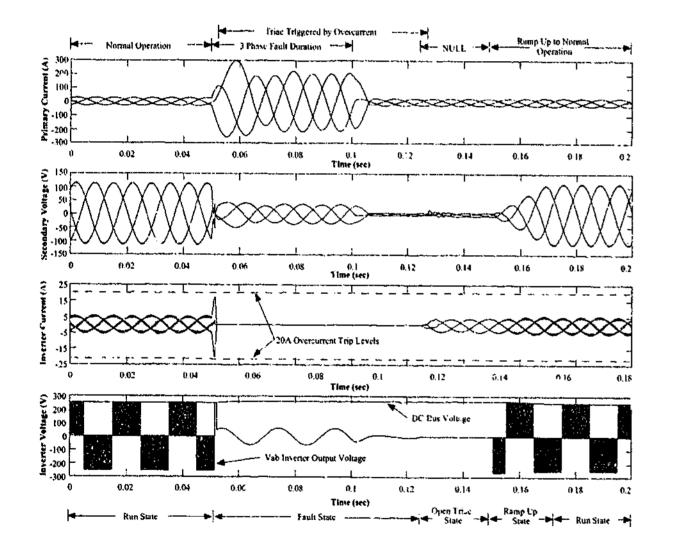

| 7.8  | Three-phase fault and recovery si   |

| 7.9  | Three phase primary fault and re    |

|      | gered protection)                   |

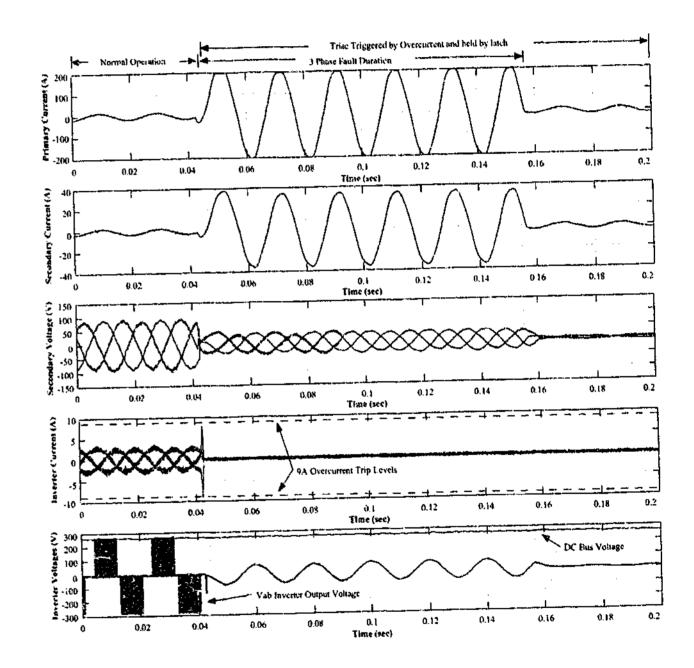

| 7.10 | 200 A-peak fault experimental res   |

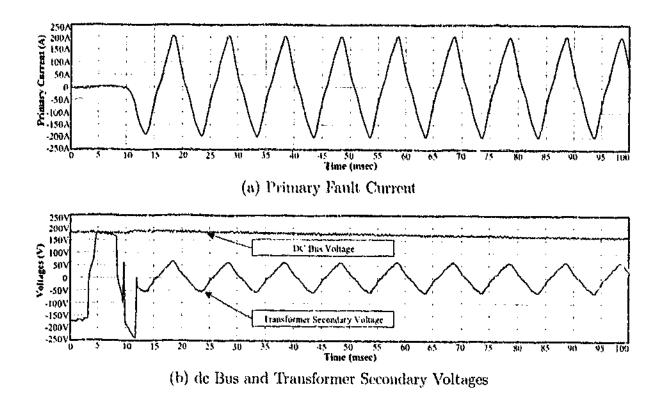

| 8.1  | Linear model (Simulink) of the se   |

| 8.2  | Simulink models used to create      |

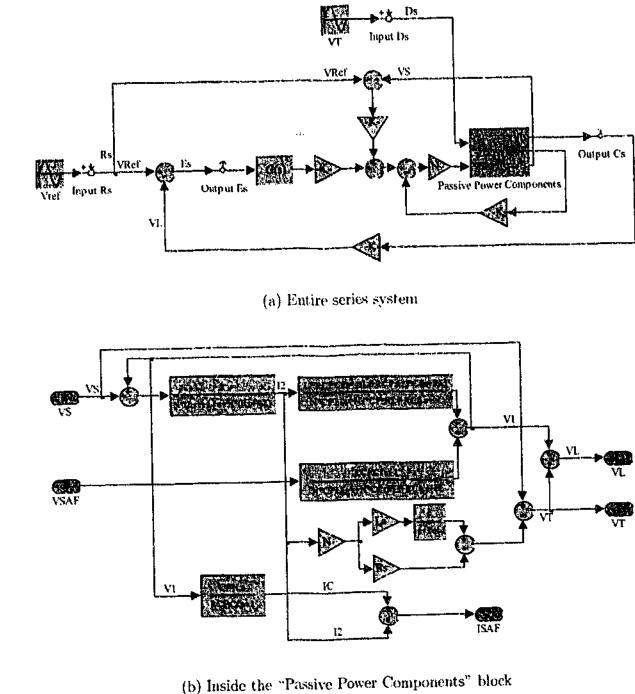

|      | systems.                            |

| 8.3  | Power System Blockset based Sin     |

| 8.4  | Series VSI sub-system shown in F    |

| 8.5  | Series controller sub-system show   |

| 8.6  |                                     |

| 8.7  |                                     |

| 8.8  | Simulated results of the UCPC co    |

|      | and supply current.                 |

| 9.1  | Components of the experimental      |

xii

| continuous, shift and delta-based, 16-bit P+Reson | ant |

|---------------------------------------------------|-----|

| •••••••••                                         | 147 |

| based P+Resonant current regulator                | 148 |

| based P+Resonant current regulator                | 148 |

| esponse for ideal continuous and delta-based 16-  |     |

| at controllers (with parameters from the series   |     |

| •••••••••••••••••••••••••••••••••••••••           | 149 |

| ection topology.                                  | 155 |

| ries inverter to an inverter trip with no series  |     |

|                                                   | 155 |

| verter, with integrated protection clements and   |     |

|                                                   | 158 |

| l current waveforms                               | 161 |

| stant graph                                       | 162 |

| te diagram                                        | 165 |

| nd fault test setup schematic                     | 167 |

| imulation (over-current protection triggered)     | 168 |

| ecovery experimental results (over-current trig-  |     |

|                                                   | 169 |

| sults (ac over-voltage triggered protection)      | 170 |

| eries controller and physical system elements.    | 175 |

| the frequency sweep simulations of the digital    |     |

|                                                   | 177 |

| nulink model of the UCPC and test grid system.    | 179 |

| Figure 8.3                                        | 180 |

| vn in Figure 8.3                                  | 180 |

|                                                   | 181 |

|                                                   | 181 |

| ompensating for a distortions in the load voltage |     |

|                                                   | 183 |

| UCPC prototype                                    | 186 |

19

:

## LIST OF FIGURES

100

No.

| 9.2  | Functional specification diagram for the Integrated Inverter Board (CS-IIB). (Cour- |     |

|------|-------------------------------------------------------------------------------------|-----|

|      | tesy of P. McGoldrick)                                                              | 188 |

| 9.3  | Photograph of CS-IIB controller hardware, with component layout diagram             | 189 |

| 9.4  | AutoCAD/3DMax rendering of the constructed back to back 30 kVA VSIs 1               |     |

| 9.5  | Winding arrangement schematic for one of the three identical single-phase series    |     |

|      | injection transformers                                                              | .95 |

| 9.6  | Photo of the UCPC magnetics. Above: Three separate single-phase multiple            |     |

|      | winding transformers. Below: Two three-phase sets of filter inductors 1             | .95 |

| 9.7  | Photo of the low voltage UCPC experimental test setup.                              | .97 |

| 9.8  | Photo of inside the UCPC prototype enclosure. Left: CS-IIB controller card used     |     |

|      | for series component. Center-Right: Busbars of the two VSIs                         | 98  |

| 9.9  | Experimental test configuration for the low voltage UCPC prototype. (a) Circuit     |     |

|      | Schematic, and (b) Photograph                                                       | 03  |

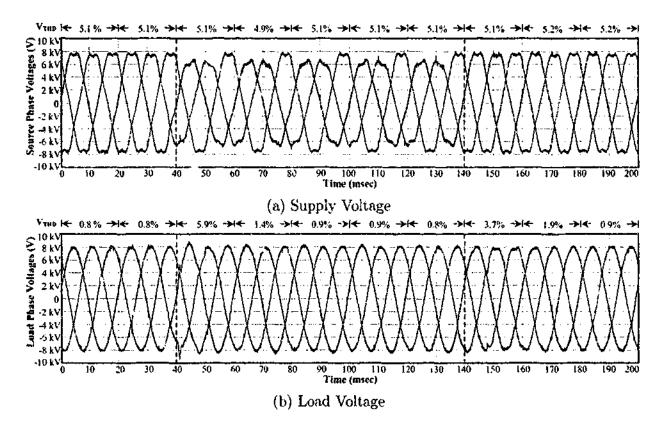

| 9.10 | Test 1 - Experimental L-L source and load voltages: (a),(c),(e) Time waveform;      |     |

|      | (b),(d),(f) Frequency spectrum                                                      | 05  |

| 9.11 | Test 2 - Experimental results of the UCPC compensating for a supply voltage         |     |

|      | with harmonics and an unbalanced fundamental component.                             | 07  |

| 9.12 | Test 3 - Experimental results of the UCPC compensating for a supply voltage         |     |

|      | with a 5 Hz 0.1 p.u. flicker component.                                             | 07  |

| 9.13 | Test 4 - Experimental results of the UCPC compensating for a 0.7 p.u. symmet-       |     |

|      | rical sag                                                                           | 09  |

| 9.14 | Test 5 - Experimental results of the UCPC compensating for a 1.2 p.u. symmet-       |     |

|      | rical swell                                                                         | 09  |

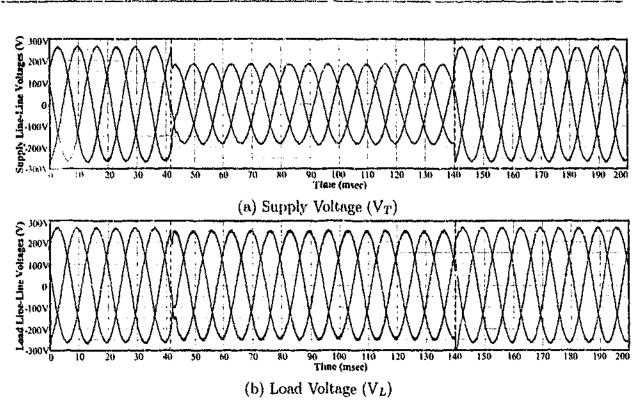

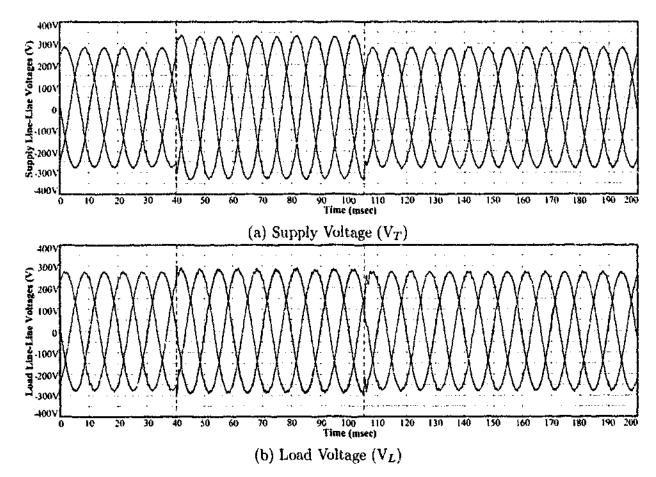

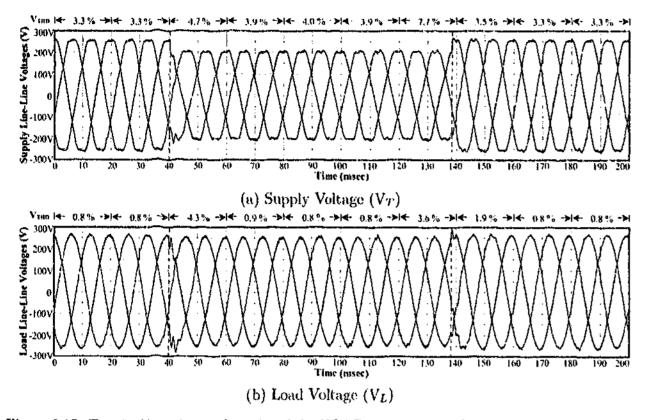

| 9.15 | Test 6 - Experimental results of the UCPC compensating for a 0.8 p.u. symmet-       |     |

|      | rical sag with harmonics                                                            | 10  |

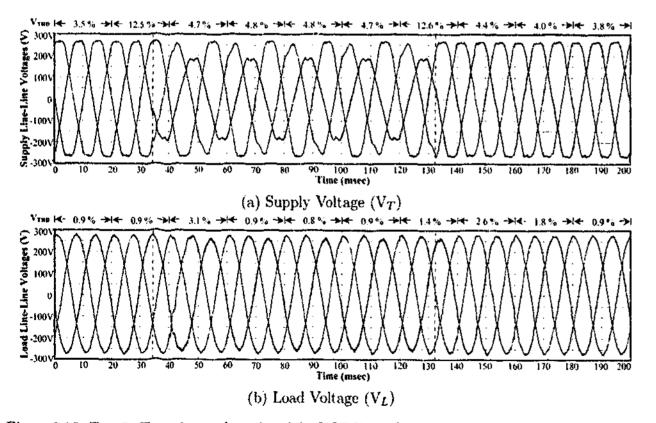

| 9.16 | Test 7 - Experimental results of the UCPC simultaneously compensating for volt-     |     |

|      | age harmonics, 0.1 p.u. 5 Hz flicker, 0.9 p.u. unbalance, and a 0.8 p.u. sag 2      | 10  |

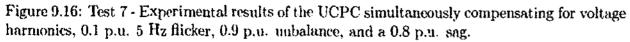

| 9.17 | Test 8 - Experimental results of the UCPC simultaneously compensating for volt-     |     |

|      | age harmonics, 0.1 p.u. 5 Hz flicker, 0.9 p.u. unbalance, and a 0.8 p.u. sag 2      | 11  |

| 9.18 | Test 8 - Experimental results of the UCPC simultaneously compensating for volt-     |     |

|      | age harmonics, 0.1 p.u. 5 Hz flicker, 0.9 p.u. unbalance, and a 0.8 p.u. sag        |     |

|      | (Zoomed view of Figure 9.17)                                                        | 11  |

### LIST OF FIGURES

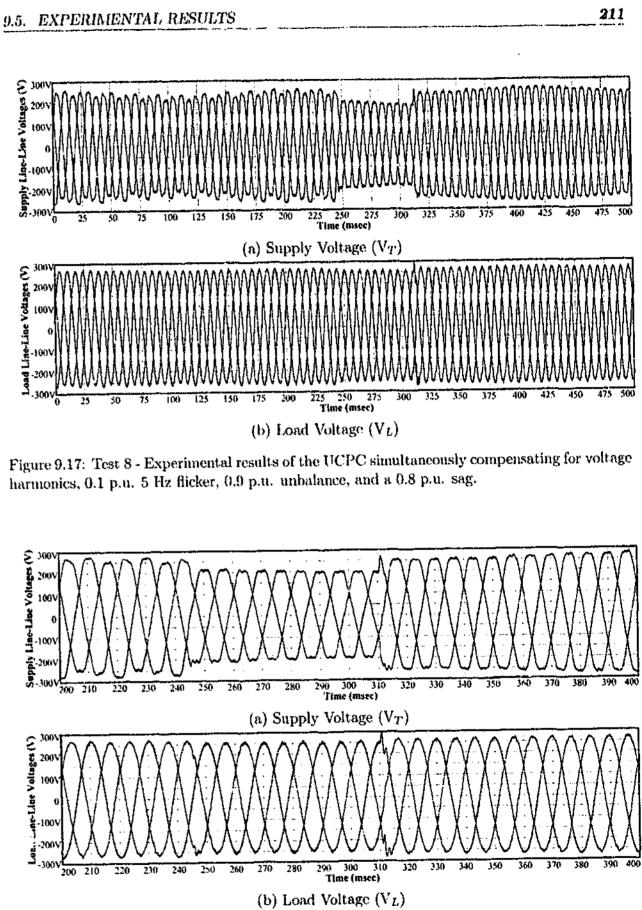

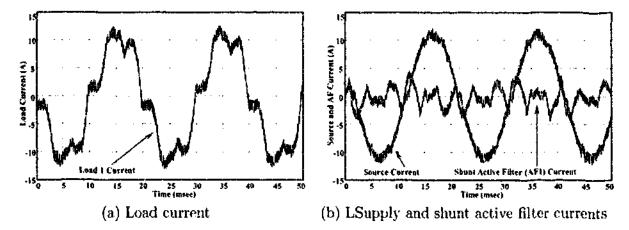

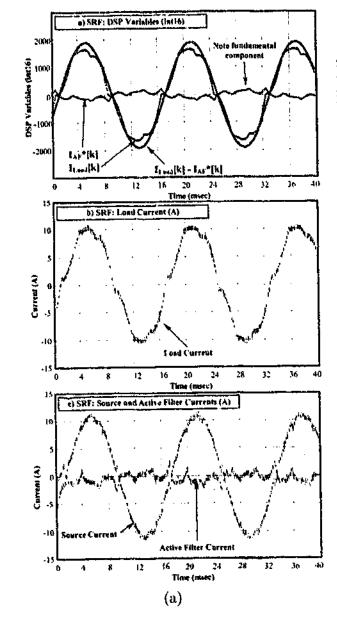

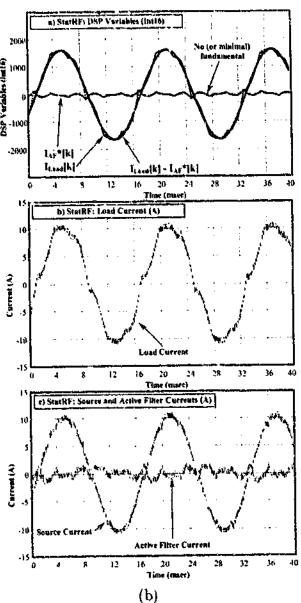

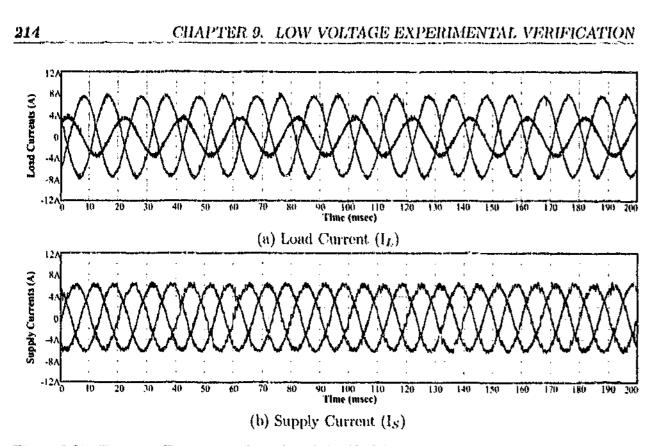

| 9.19 Test 1 - Experimental source, load |

|-----------------------------------------|

| (b),(d) frequency spectrums             |

| 9.20 Test 9 - Comparison SRF and Sta    |

| 9.21 Test 10 - Experimental results of  |

| unbalanced load currents                |

|                                         |

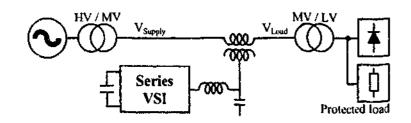

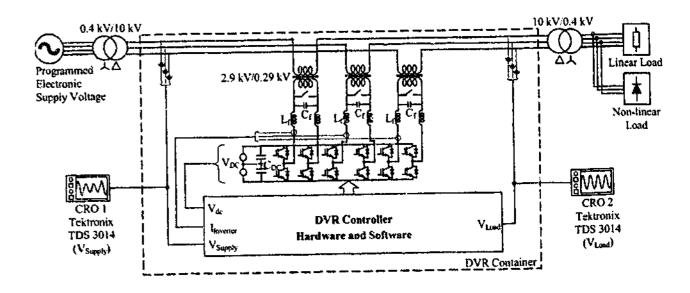

| 10.1 Series topology of the Dynamic V   |

| 10.2 Experimental DVR test system and   |

| 10.3 Photo of the DVR container and     |

| the supply and load. Location: A        |

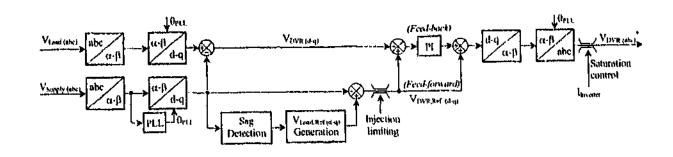

| 10.4 Existing sag compensation portion  |

| harmonic voltage compensation).         |

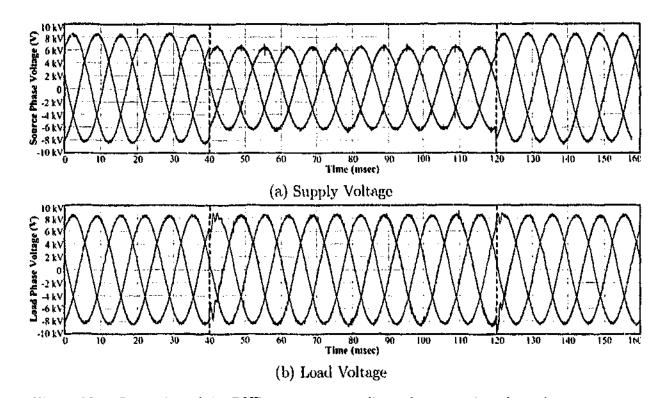

| 10.5 Operation of the DVR to a $0.76$ p |

| 10.6 Operation of the DVR to a $0.76$ p |

| harmonic compensation.                  |

| 10.7 Circuit and control block diagram  |

| and the experimental power syste        |

| 10.8 Simulated open loop frequency re   |

| and (b) the series injection syster     |

| 10.9 Simulated supply voltage disturb   |

| proposed harmonic controllers.          |

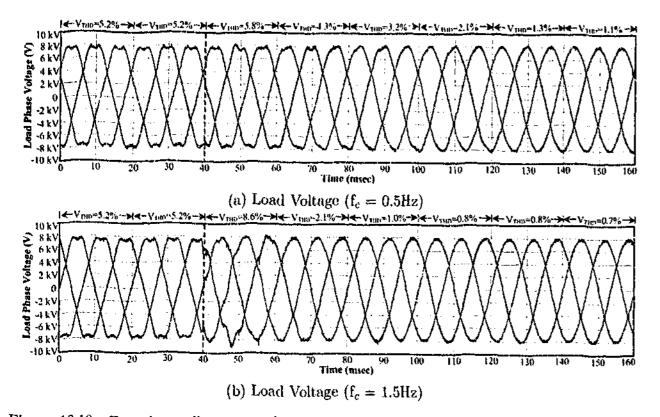

| 10.10Experimentally measured startup    |

| pensation controllers.                  |

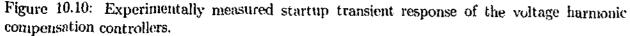

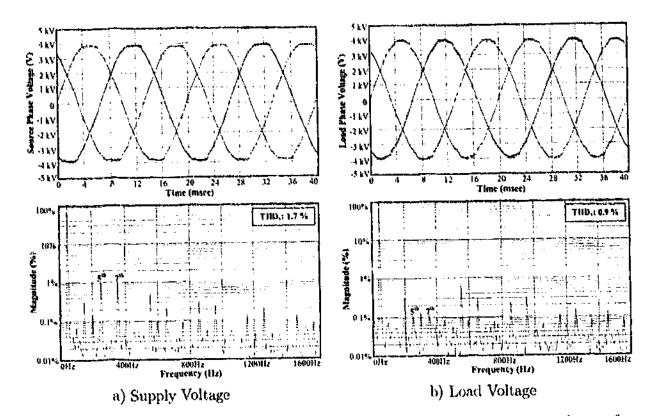

| 10.11Experimentally measured steady     |

| mance in time and frequency dom         |

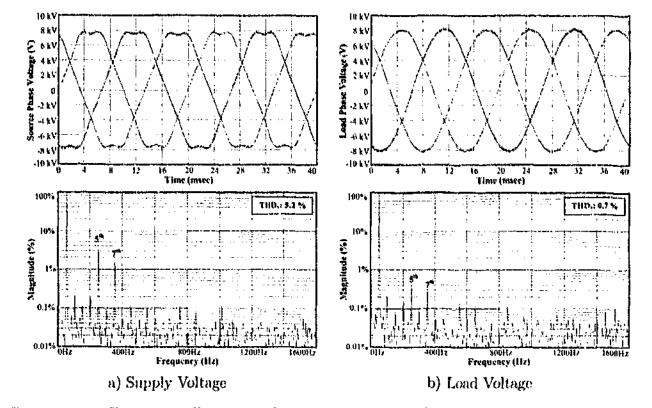

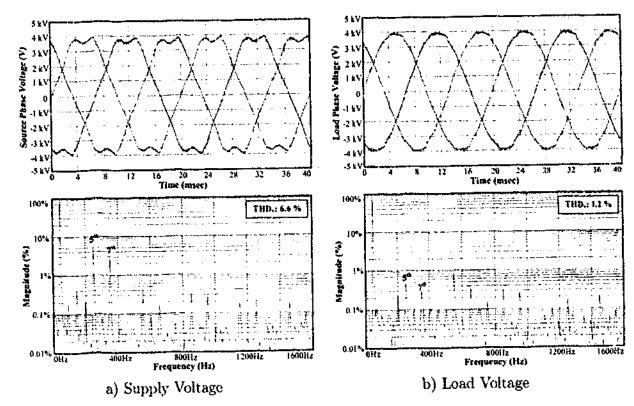

| 10.12Experimentally measured steady     |

| mance in time and frequency don         |

| 10.13Experimentally measured steady     |

| mance in time and frequency don         |

| 10.14Experimentally measured steady     |

| mance in time and frequency dor         |

| load                                    |

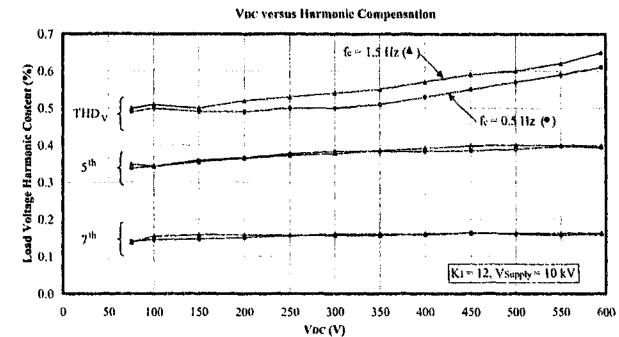

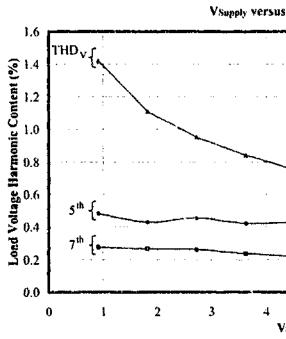

| 10.15Experimentally measured results    |

| and (b) supply voltage, to highlig      |

|                                         |

|                                         |

xiv

| ad and active filter current (a),(c)waveforms and                  |  |

|--------------------------------------------------------------------|--|

|                                                                    |  |

| tatRF harmonic extraction implementations 213                      |  |

| f the UCPC balancing the supply current due to                     |  |

|                                                                    |  |

| Voltage Restorer (DVR) 218                                         |  |

| and measurement setup                                              |  |

| d the 10 kV/0.4 kV distribution tranformers for                    |  |

| Aalborg University, Denmark                                        |  |

| on of the control structure (i.e. not including the                |  |

| )                                                                  |  |

| p.u. dip with no supply voltage harmonics 224                      |  |

| $\delta$ p.u. dip with supply voltage harmonics and no             |  |

|                                                                    |  |

| am of the DVR (placed in a 20 foot container),                     |  |

| tem test setup                                                     |  |

| response of the (a) voltage harmonic controllers,                  |  |

| em (both control and plant)                                        |  |

| bance rejection from the load voltage due to the                   |  |

|                                                                    |  |

| p transient response of the voltage harmonic com-                  |  |

|                                                                    |  |

| ly-state voltage harmonic compensation perfor-                     |  |

| omains: Source voltage distortion ( $f_{sw} = 3$ kHz). 232         |  |

| ly-state voltage harmonic compensation perfor-                     |  |

| mains: Source voltage distortion ( $f_{sw} = 5 \text{ kHz}$ ). 232 |  |

| ly-state voltage harmonic compensation perfor-                     |  |

| omains: Non-linear load                                            |  |

| ly-state voltage harmonic compensation perfor-                     |  |

| omains: Source voltage distortion and non-linear                   |  |

|                                                                    |  |

| ts of the DVR with varying, (a) dc-bus voltage,                    |  |

| ight the effect of varying the modulation depth. 235               |  |

|                                                                    |  |

•••

٠

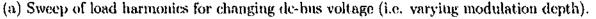

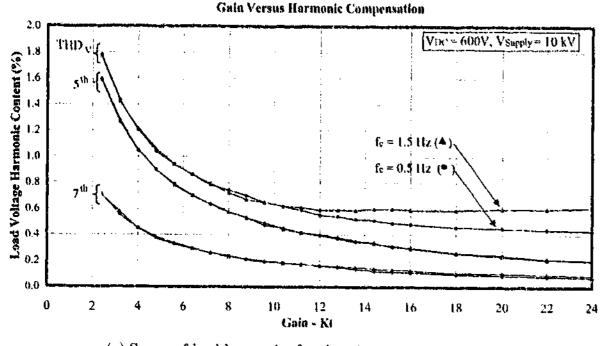

| 10.16Experimentally measured results of the DVR with varying gain. Figure (a) shows          |

|----------------------------------------------------------------------------------------------|

| the actual harmonic content, and (b) is the attenuation relative to the original             |

| supply harmonics                                                                             |

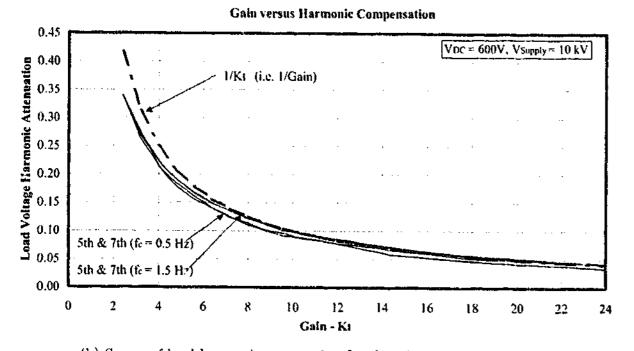

| 10.17Simulated inverter output voltage disturbance rejection from the load voltage due       |

| to the proposed harmonic controllers                                                         |

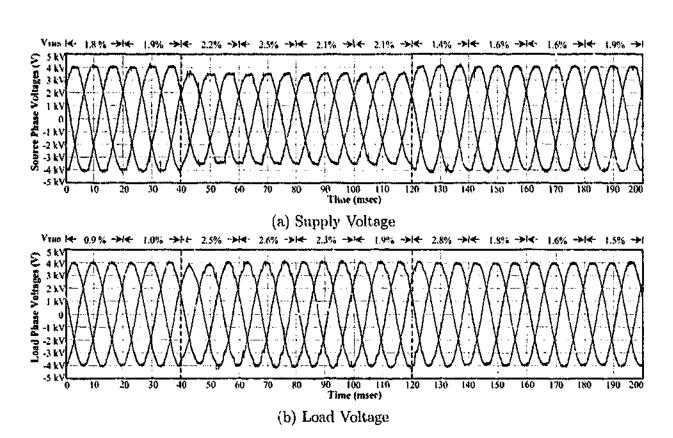

| 10.18Experimentally measured results of the DVR with $5^{th}$ and $7^{th}$ voltage harmonic  |

| compensation for a dip with supply voltage harmonics and linear load 239                     |

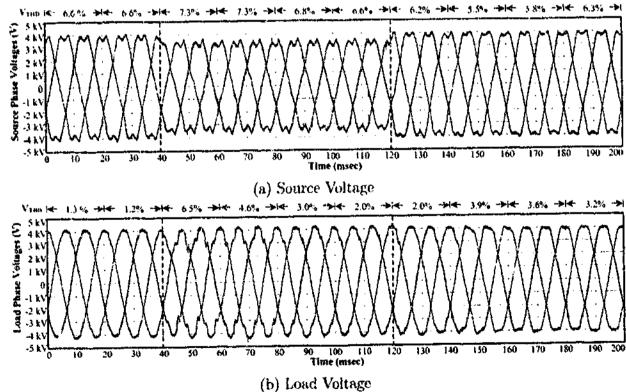

| 10.19Experimentally measured results of the DVR with $5^{th}$ and $7^{th}$ voltage harmonic  |

| compensation for a dip with supply voltage harmonics and non-linear load 239                 |

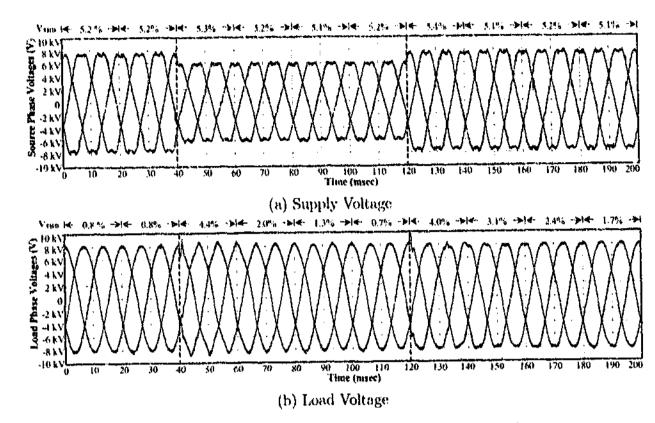

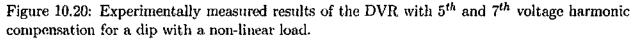

| 10.20 Experimentally measured results of the DVR with $5^{th}$ and $7^{th}$ voltage harmonic |

| compensation for a dip with a non-linear load.                                               |

| 10.21 Experimentally measured results of the DVR with $5^{th}$ and $7^{th}$ voltage harmonic |

| compensation for an un-symmetrical dip with supply voltage harmonics 240                     |

| A.1 Example waveforms of type 2 to type 6 Power Quality problems                             |

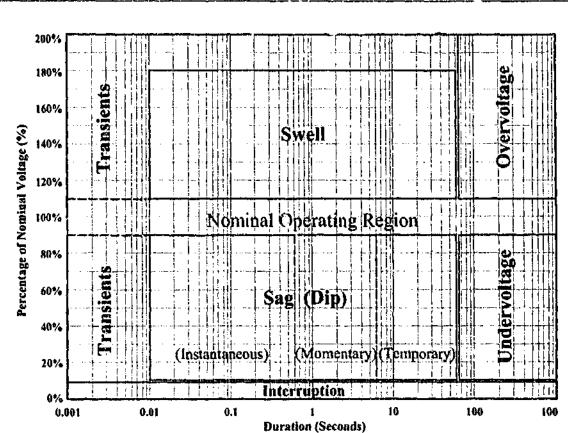

| A.2 Diagrammatic classification of long (type 2) and short (type 3) duration voltage         |

| fluctuations.                                                                                |

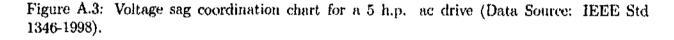

| A.3 Voltage sag coordination chart for a 5 h.p. ac drive (Data Source: IEEE Std              |

| 1346-1998)                                                                                   |

| A.4 Comparison of ITIC curve and limits specified by the Victorian Distribution Code.259     |

# List of Tables

- 2.2 Review of selected Custom Power compensation capabilities of the passive hybrid topologies). Note and compensation capabilities of

- 2.3 Existing acronyms for combined

- 2.4 Review of combined series-shunt Power Quality compensation cap grey background indicates the p system which are preferred by this

- 4.1 Series model parameter types.

- 5.1 Control and series converter para

- 6.1 2<sup>nd</sup> order delta and shift coefficie

- 6.2 Parameters of the delta-based III back compensation. . . . . .

- 6.3 Comparison of digital filtering te of narrowband type controllers.

- 9.1 Load voltage harmonics before a

- 10.1 Main specifications of the experim

- 10.2 Steady-state test results of the lo

| 2.2  | Review of selected Custom Power research outlining the reported Power Quality      |     |

|------|------------------------------------------------------------------------------------|-----|

|      | compensation capabilities of the shunt (parallel) and series topologies (including |     |

|      | passive hybrid topologies). Note that a grey background indicates the physical     |     |

|      | and compensation capabilities of each system which are preferred by this research. | 19  |

| 2.3  | Existing acronyms for combined series-shunt Custom Power devices                   | 24  |

| 2.4  | Review of combined series-shunt Custom Power research outlining the reported       |     |

|      | Power Quality compensation capabilities of each proposed device. Note that a       |     |

|      | grey background indicates the physical and compensation capabilities of each       |     |

|      | system which are preferred by this research.                                       | 25  |

| 4.1  | Series model parameter types                                                       | 61  |

| 5.1  | Control and series converter parameters for the LV experimental work.              | 102 |

| 6.1  | $2^{nd}$ order delta and shift coefficient conversions.                            | 135 |

| 6.2  | Parameters of the delta-based IIR digital filters used for the UCPC series feed-   |     |

|      | back compensation.                                                                 | 149 |

| 6.3  | Comparison of digital filtering techniques for 16bit fixed-point implementations   |     |

|      | of narrowband type controllers.                                                    | 151 |

| 9.1  | Load voltage harmonics before and after series injection                           | 206 |

| 10.1 | Main specifications of the experimental DVR.                                       | 220 |

| 10.2 | Steady-state test results of the load voltage harmonics before and after compen-   |     |

|      | sation                                                                             | 230 |

| A.1  | Catagories of power system Power Quality phenomena [18].                           | 253 |

xvii

#### LIST OF TABLES

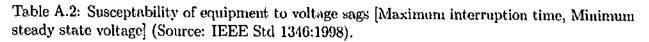

| A.2        | Susceptability of equipment to voltage sags [Maximum interruption time, Mini-      |     |

|------------|------------------------------------------------------------------------------------|-----|

|            | mum steady state voltage] (Source: IEEE Std 1346:1998).                            | 256 |

| A.3        | Normalised average voltage sag data from EPRI study incorporating 222 distribu-    |     |

|            | tion feeders for 2 years. Nominal value is 50.2 events per site per year. (Adapted |     |

|            | from IEEE Std 1346:1998)                                                           | 257 |

| B.1        | Default design parameters for stability model tests.                               | 263 |

| <b>B.2</b> | Final parameters used for the LV experimental work.                                | 264 |

| <b>B.3</b> | Parameters of the delta-based IIR digital filters used for the UCPC series feed-   |     |

|            | back compensation.                                                                 | 265 |

| B.4        | Nameplate and measured specifications of the LV experimental single-phase scries   |     |

|            | injection transformers.                                                            | 266 |

|            |                                                                                    |     |

## Abstract

にはないのでは、「ない」の「ような」」というと

The cost to society due to poor electrical power quality takes the form of physical damage, nuisance, and financial consequences. In recent years the dramatic cost reduction of higher power static devices has enabled the use of power electronics to become a financially viable solution to rectifying poor power quality in areas of most need. This range of applications is known as Custom Power.

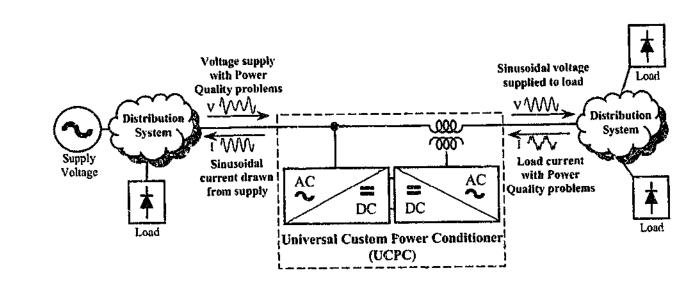

This thesis presents the design and control processes for a Custom Power application using the combined series-shunt topology, and is called the Universal Custom Power Conditioner, or UCPC. The series-shunt back-to-back power converter topology offers the flexibility to simultaneously regulate both load voltage and supply current. However, the ability of the device to compensate for Power Quality problems is dependent on the rating of the two power converters and the performance of the control systems.

It is shown that by rating the UCPC to only half the load power requirements, the device is still able to compensate for the majority of Power Quality events, without the need for large energy storage capabilities. For higher power systems the UCPC may therefore be a more cost effective option compared to systems which require full per unit ratings and large energy storage capabilities (which also leads to large maintenance costs).

Due to the strict transient and steady-state performance requirements that are necessary for adequate compensation of Power Quality events, the converter control systems are key to the performance of the UCPC, and are therefore a primary focus of this work. The aspects of control considered are: the primary control systems for both the series and shunt power converters, the digital control aspects, and the control of the series converter protection system.

The proposed control system allows the series section of the UCPC to compensate for deviations in the load voltage, including fundamental magnitude, harmonics, unbalance, sags, swells, phase jump, and flicker. The shunt section of the UCPC compensates for harmonics and unbalance in the supply current, and also controls the power flow to the common dc-bus. The series control system applies stationary frame P+Resonant controllers to this topology for the first

xix

time, to provide improved steady-state compensation compared to existing systems, and to allow for both three-phase and single-phase operation whilst keeping the practical computational overheads to a minimum. This stationary frame form of controller is applied to the fundamental,  $5^{th}$ ,  $7^{th}$   $9^{th}$ ,  $11^{th}$  and  $13^{th}$  voltage harmonics, and is used in combination with feed-forward and active damping controllers to maintain good transient performance and stability, respectively. For the shunt controller, a deadbeat current regulation scheme is used. However, to create the reference signal for this controller a new stationary frame reference generation system was developed that provides improved computational advantages (using the same methodology as was used for the development of the P+Resonant controller), and is applicable to single-phase systems (unlike the synchronous *d-q* frame equivalent).

This thesis also investigates the digital implementation of the proposed systems and identifies the use of delta operator based Infinite Impulse Response (IIR) digital filters for use with realtime control of power converters. This provides a solution to the known problems associated with the digital implementation of stationary frame linear controllers on 16-bit fixed-point processors.

The control of the protection systems for the UCPC is the final control aspect investigated. An integrated protection system for the series topology is proposed to ensure a continuous, appropriately rated, current path under fault conditions, as well as start-up, stand-by, shutdown and recovery from faults.

The UCPC and all of the related theoretical concepts and control systems have been extensively verified in simulation, low voltage experimental work, and in a medium voltage experimental prototype of the series component.

## Declaration

This thesis contains no material which has been accepted for the award of any other degree or diploma in any university or other institution, and to the best of the author's knowledge, contains no material previously published or written by another person, except where due reference is made in the text of the thesis.

Michael John Newman

Declaration

# Acknowledgements

The last few years of working on a PhD has opened up my perspective on life, has allowed me to travel more, and given me the opportunity to meet new people who have also contributed towards this work in many ways. I would firstly like to thank my supervisor Assoc. Prof. Grahame Holmes. It has been a privilege to work with you and the close knit research group you have spent so much time to develop. It is hard to imagine a PhD without a wrong path here and there, but if I could make my choice of supervisor again, I would choose you again as the one to help guide me down this blind path reserved only for PhD students.

To my office mates, Dr. Daniel Zmood and Dr. Brendan McGrath, thank-you for keeping me on track, the insightful group discussions, and your friendship. Thank-you to Andrew McIver who was there without fail to answer my hardware and software questions; you definitely have 'the knack'. To Pat McGoldrick, I give thanks for your friendship, technical support, and help with all the little bits that get things done. Thank-you to Martin Lizner for help with the metal work, and to Linda, Pat, Erika, Brendan and Dan, who took the time to proof-read this thesis. A special thank-you goes to Prof. Frede Blaabjerg of Aalborg University, Denmark. Your trust in letting me work with your medium voltage experimental system is truly appreciated. Thank-you also for your continued support long after my departure from Denmark. It has been an honor and pleasure to work both with you and your research group. For rebuilding the system I thank its creator, Dr. John Godsk Nielsen, who took time off work to help me get started. Thanks to Assoc. Prof. Hans Nielsen, and the technical staff, Walter and Kim, for their help.

To Gert, Christian, Christinel and Remus, thank-you for making me feel at home in Aalborg.

Last, but not least, I would like to thank my family. To my parents, Lorraine and Adrian, I dedicate this thesis. I am indebted for the unconditional support and encouragement you have given throughout my entire education. Thank-you to my beautiful, caring and intelligent fiance, Debbie. I love you. Some questioned the sanity of us working simultaneously on our PhDs, but doing so has allowed us to grow closer and identify with each other's daily PhD woes. With this chapter of our lives coming to an end, we can now start our next adventure in life.

# **Publications**

Several parts of the work and ideas presented in this thesis have been published by the author during the course of the research work. These publications are listed below.

#### **IEEE Transactions**

- 679-687, 2002.

- Nov./Dec., pp. 1591-1599, 2002.

- 2003.

- Trans. on Ind. Applicat. (In Review)

- plies," IEEE Trans. on Pow. Elect., vol. 18, no. 5, Sept., 2003.

- (Accepted for Publication)

[1] M.J. Newman and D.G. Holmes, "An Integrated Approach for the Protection of Series Injection Inverters," IEEE Trans. on Ind. Applicat., vol. 38, no. 3, May/June, pp.

[2] M.J. Newman, D.N. Zmood, and D.G. Holmes, "Stationary Frame Harmonic Reference Generation for Active Filter Systems," IEEE Trans. on Ind. Applicat., vol. 38, no. 6,

[3] M.J. Newman and D.G. Holmes, "Delta Operator Digital Filters for High Performance Inverter Applications," IEEE Trans. on Pow. Elect., vol. 18, no. 1, Jan., pp. 447-454,

[4] M.J. Newman, D.G. Holmes, J.G. Nielsen, and F. Blaabjerg, "A Dynamic Voltage Restorer (DVR) with Selective Harmonic Compensation at Medium Voltage Level," IEEE

[5] P.C. Loh, M.J. Newman, D.N. Zmood, and D.G. Holmes, "Improved Transient and Steady State Voltage Regulation for Single and Three Phase Uninterruptible Power Sup-

[6] J.G. Nielsen, M.J. Newman, H.N. Nielsen, and F. Blaabjerg, "Control and Testing of a Dynamic Voltage Restorer at Medium Voltage Level," IEEE Trans. on Pow. Elect.

ため、方では、「ない」となった。「ない」というないで、ないないないで、「ない」というで、私にないない。

**IEEE Conference Proceedings**

- [7] M.J. Newman and D.G. Holmes, "An Integrated Approach for the Protection of Series Injection Invertors," in Conf. Rec. IEEE/IAS Annual Meeting, Chicago, IL, USA, pp. 781-788, 2001.

- [8] M.J. Newman, D.N. Zmood, and D.G. Holmes, "Stationary Frame Harmonic Reference Generation for Active Filter Systems," in Conf. Rec. IEEE/APEC, Dallas, TX, pp. 1054-1060, 2002.

- [9] M.J. Newman and D.G. Holmes, "Delta Operator Digital Filters for High Performance Inverter Applications," in Conf. Rec. IEEE/PESC, Cairns, Qld, Australia, pp. 1407-1412, 2002.

- [10] M.J. Newman and D.G. Holmes, "A Universal Custom Power Conditioner (UCPC) with Selective Harmonic Compensation," in Conf. Rec. IEEE/IECON, Seville, Spain, Nov. 2002.

- [11] M.J. Newman, D.G. Holmes, J.G. Nielsen, and F. Blaabjerg, "A Dynamic Voltage Restorer (DVR) with Selective Harmonic Compensation at Medium Voltage Level," in Conf. Rec. IEEE/IAS, Salt Lake City, UT, 2003. (In Print)

- [12] P.C. Loh, M.J. Newman, D.N. Zmood, and D.G. Holmes, "Improved Transient and Steady State Voltage Regulation for Single and Three Phase Uninterruptible Power Supplies," in Conf. Rec. IEEE/PESC, Vancouver, BC, Canada, pp. 498-503, 2001.

- [13] J.G. Nielsen, M.J. Newman, H.N. Nielsen, and F. Blaabjerg, "Control and Testing of a Dynamic Voltage Restorer at Medium Voltage Level," in Conf. Rec. IEEE/PESC Annual Meeting, Acapulco, Mexico, 2003.

- [14] G.H. Bode, M.J. Newman, D.G. Holmes, "Design and Analysis of Robust Predictive Current Regulated Algorithms," in Conf. Rec. IEEE/PEDS, Singapore, 2003. (In Print)

- [15] E. Twining, M.J. Newman, P.C. Loh, D.G. Holmes, "Voltage compensation in weak distribution networks using a D-Statcom", in Conf. Rec. IEEE/PEDS, Singapore, 2003. (In Print)

## **Glossary of Terms**

| A/D   | Analog to Digital conversion             |

|-------|------------------------------------------|

| AF    | Active Filter                            |

| ANSI  | American National Standards              |

| APLC  | Active Power Line Conditione             |

| BJT   | <b>Bipolar Junction Transistor</b>       |

| CT    | Current Transformer                      |

| CRO   | Cathode Ray Oscilloscope                 |

| DC    | Direct Current                           |

| DF    | Direct Form digital filter stru          |

| DFT   | Discrete Fourier Transform               |

| DSP   | Digital Signal Processor                 |

| DVR   | Dynamic Voltage Restorer                 |

| FACTS | Flexible AC Transmission Sys             |

| FIR   | Finite Impulse Response                  |

| FWL   | Finite Word Length                       |

| HP    | High Pass                                |

| ΗV    | High Voltage System ( $> 66$             |

| IEC   | International Electrotechnica            |

| IEE   | The Institution of Electrical            |

| IEEE  | The Institute of Electrical an           |

| IIR   | Infinite Impulse Response                |

| IGBT  | Insulated Gate Bipolar Trans             |

| ITIC  | Information Technology Indu              |

| LC    | Inductor-Capacitor 2 <sup>nd</sup> order |

| LV    | Low Voltage System ( 110 V               |

|       |                                          |

ls Institute ıer

ucture (i.e. DFI, DFIt, DFII, DFIIt)

/stem

kV) al Commission Engineers nd Electronics Engineers

sistor ustry Council er filter - 415 V )

xxvii

| LVRC           | Line Voltage Regulator/Conditioner                   |

|----------------|------------------------------------------------------|

| MATLAB         | Numerical Analysis Program                           |

| MUPC           | Multilevel Universal Power Conditioner               |

| MV             | Medium Voltage System ( 6 kV - 66 kV )               |

| P∔R            | Proportional plus Resonant Control (i.e. P+Resonant) |

| PAF            | Shunt/Parallel Active Filter                         |

| PCC            | Point of Common Coupling                             |

| PCR            | Predictive Current Regulation                        |

| PDPINT         | Power Drive Protection Interrupt                     |

| PI             | Proportional Integral Control                        |

| PLL            | Phase Lock Loop                                      |

| PLC            | Power Line Conditioner                               |

| РМ             | Phase Margin                                         |

| PWM            | Pulse Width Modulation                               |

| SAF            | Series Active Filter                                 |

| SEMI           | Semiconductor Equipment and Materials International  |

| SRF            | Synchronous Reference Frame                          |

| StatRF         | Stationary Reference Frame                           |

| STATCOM        | Static Synchronous Compensator                       |

| SVC            | Static Var Compensator                               |

| TCR            | Thyristor Controlled Reactor                         |

| THD            | Total Harmonic Distortion                            |

| UCPC           | Universal Custom Power Conditioner                   |

| UPFC           | Universal Power Flow Controller                      |

| UPLC           | Universal Active Power Line Conditioner              |

| UPQC           | Unified Power Quality Conditioner                    |

| UPQM           | Universal Power Quality Manager                      |

| UPS            | Uninterruptable Power Supply                         |

| USSC           | Universal Series Shunt Conditioner                   |

| $\mathbf{VSI}$ | Voltage Source Inverter                              |

|                |                                                      |

# List of Symbols Used

### Lowercase Greek

| α               | First phase quality in the ortho     |  |

|-----------------|--------------------------------------|--|

| $\alpha_k$      | Delta IIR digital filter denomin     |  |

| β               | Second phase quality in the ort      |  |

| $\beta_k$       | Delta IIR digital filter numerat     |  |

| γ               | Gamma (discrete version of the       |  |

| δ               | Delta operator                       |  |

| $\delta^{-1}$   | Inverse delta operator               |  |

| T Delay         | Delay in control system loop de      |  |

| $\phi_L$        | Phase angle of the load current      |  |

| $\phi_n$        | Phase offset for the $n^{th}$ harmon |  |

| $\phi_{SAF}$    | Phase angle of series injected v     |  |

| $\phi_{SAG}$    | Voltage sag phase jump angle         |  |

| $\omega_0$      | Fundamental frequency (rad/se        |  |

| $\omega_c$      | Cut-off frequency (rad/sec)          |  |

| $\omega_n$      | $n^{th}$ harmonic frequency (rad/set |  |

| Uppercase Greek |                                      |  |

- Sample time / free design variable Δ

logonal  $\alpha$ - $\beta$  reference frame nator coefficients thogonal  $\alpha$ - $\beta$  reference frame tor coefficients he Laplace 's')

due to digitization nt  $(I_L)$ mic controller voltage

sec)

sec)

$\Delta T$  Switching period time (i.e. half full switching cycle for asymmetrical PWM)

List of Symbols Used

| Lowercase                     |                                                                                |

|-------------------------------|--------------------------------------------------------------------------------|

| a                             | First phase of a three-phase system (sometimes denoted as the red phase)       |

| $a_k$                         | Shift IIR digital filter denominator coefficients                              |

| ь                             | Second phase of a three-phase system (sometimes denoted as the white phase)    |

| $b_k$                         | Shift IIR digital filter numerator coefficients                                |

| С                             | Third phase of a three-phase system (sometimes denoted as the blue phase)      |

| $f_0$                         | Fundamental frequency (Hz)                                                     |

| fbreak                        | Break point frequency of the LC filter                                         |

| $f_c$                         | Cut-off frequency (Hz)                                                         |

| $f_n$                         | $n^{th}$ harmonic frequency (Hz)                                               |

| fs                            | Sample frequency of the digital controller                                     |

| $f_{sw}$                      | Switching frequency of the PWM                                                 |

| $h_{dq}(t)$                   | Analog time-domain filter function referred to the $d-q$ reference frame       |

| п                             | Harmonic number (i.e. $n^{th}$ harmonic). Mainly used in subscripts.           |

| q                             | Shift operator                                                                 |

| $t_{SAG}$                     | Voltage sag time duration (seconds)                                            |

| $t_{SAG,Max}$                 | Maximum sag compensation duration by the UCPC for given conditions             |

| w[t]                          | Windowing function for FIR digital filter creation                             |

| x[k]                          | Discrete input sequence                                                        |

| $x_{lpha}(t),  x_{eta}(t)$    | $\alpha \& \beta$ phase input variables ( $\alpha$ - $\beta$ reference frame)  |

| $x_a(t), x_b(t)$              | a & b phase input variables ( <i>abc</i> reference frame)                      |

| y[k]                          | Discrete output sequence                                                       |

| $y_{\alpha}(t), y_{\beta}(t)$ | $\alpha \& \beta$ phase output variables ( $\alpha$ - $\beta$ reference frame) |

| $y_a(t),y_b(t)$               | a & b phase output variables (abc reference frame)                             |

| U | ppercase |

|---|----------|

|   |          |

| oppercase                       |                                     |

|---------------------------------|-------------------------------------|

| C(s)                            | Target output parameter for         |

| $C_{DC}$                        | Capacitance located across t        |

| $C_F$                           | Filter capacitance $(X = _{SAF} f$  |

| D(s)                            | Disturbance input for a cont        |

| E(s)                            | Error term for a control syst       |

| $G_1(s)$                        | Feed-back linear series contr       |

| $G_2(s)$                        | s-domain model of the series        |

| $[\mathbf{H}_{ab}(\mathbf{s})]$ | 2 x 2 Matrix of Analog cross        |

| $H_{dq}(s)$                     | Analog s-domain filter funct        |

| $H_{\delta}(\gamma)$            | Delta operator $(\delta)$ based Inf |

| $H_q(z)$                        | Shift operator $(q)$ based Infi     |

| $I_L$                           | Load current                        |

| $I_{L,SAG}$                     | Load current during a volta         |

| I <sub>PAF</sub>                | Output current of the shunt         |

| $I_{PAF}^{*}$                   | Demanded output current o           |

| I <sub>Trip</sub>               | Minimum current in the series       |

| $K_{AD}$                        | Series active damping gain o        |

| $K_I$                           | Integral gain constant              |

| $K_{l,n}$                       | Integral gain constant for th       |

| K <sub>P</sub>                  | Proportional gain constant          |

| $L_{F,X}$                       | Filter inductance $(X = SAF)$       |

| $L_{Load}$                      | Load inductance                     |

| $L_S$                           | Source inductance                   |

| N                               | Series transformer ratio            |

| Pav                             | Average power dissipation           |

| $P_{DC,NET}$                    | Net real power flow out of t        |

| $P_{PAF}$                       | Real power flow out of the s        |

| $P_{SAF}$                       | Real power flow out of the s        |

| $Q_{PAF}$                       | Reactive power flow out of          |

| $Q_{SAF}$                       | Reactive power flow out of          |

|                                 |                                     |

XXX

1

.

- or a control system

- the cic-bus

- for scries inverter, and X = PAF for parallel inverter)

- itrol system

- stem

- roller

- es system plant

- as coupled filters between the a & b phases

- tion referred to the d-q reference frame

- finite Impulse Response (IIR) digital filter

- finite Impulse Response (IIR) digital filter

- age sag (only applies for In-phase compensation ) at (parallel) inverter of the shunt (parallel) inverter

- ries clamping varistor required to trip the protection

- constant

- he n<sup>th</sup> harmonic

- for series inverter, and X = PAF for parallel inverter)

- the dc-bus energy storage shunt (parallel) converter series converter the shunt (parallel) converter

- the series converter

xx di

| R(s)                           | Reference input to a control system                                               |

|--------------------------------|-----------------------------------------------------------------------------------|

| $R_{CF}$                       | Resistance in series with the filter capacitance, $C_F$                           |

| $R_{LF}$                       | Internal series resistance of the filter inductor, $L_F$                          |

| R <sub>Load</sub>              | Load resistance                                                                   |

| $R_S$                          | Source resistance                                                                 |

| T                              | Discrete sample time constant (sec)                                               |

| $V_{DC}$                       | Voltage of the common dc-bus                                                      |

| $V_L$                          | Load voltage                                                                      |

| $V_{PAF}^*$                    | Demanded voltage by the shunt PCR controller for the PWM generator                |

| $V_{Rej}$                      | Reference load voltage for the series controller                                  |

| $V_S$                          | Source voltage (i.e. before source impedance)                                     |

| $V_{SAF}^*$                    | Demanded voltage by the series control system for the PWM generator               |

| $V_{SAF,Normalised}^*$         | $V_{SAF}^*$ normalized to a modulation depth using the measured value of $V_{DC}$ |

| $V_T$                          | Terminal supply voltage (i.e. after source impedance)                             |

| $V_{T,SAG}$                    | Terminal supply voltage during a voltage sag event                                |

| $V_{T\tau ip}$                 | Peak ac voltage at which the series protection will trip                          |

| $X_{\alpha}(s),  X_{\beta}(s)$ | $\alpha \& \beta$ phase input variables ( $\alpha$ - $\beta$ reference frame)     |

| $X_a(s), X_b(s)$               | a & b phase input variables ( <i>abc</i> reference frame)                         |

| $Y_{\alpha}(s),  Y_{\beta}(s)$ | $\alpha \& \beta$ phase output variables ( $\alpha$ - $\beta$ reference frame)    |

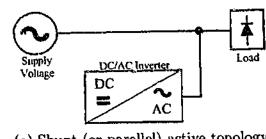

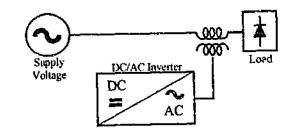

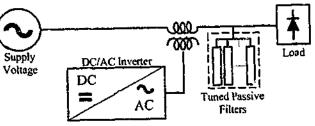

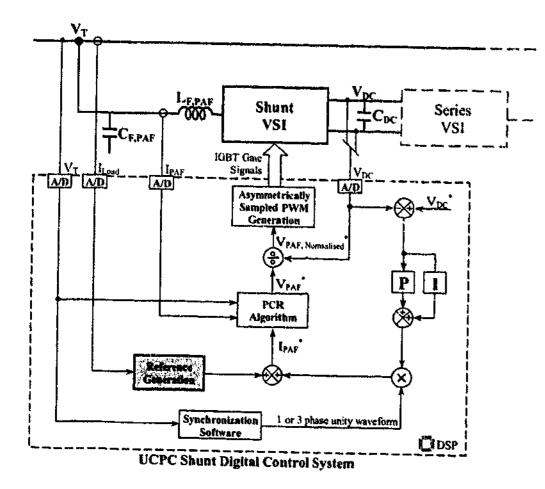

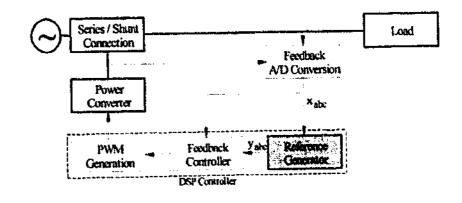

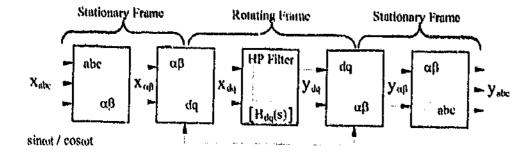

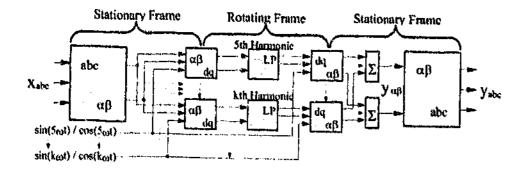

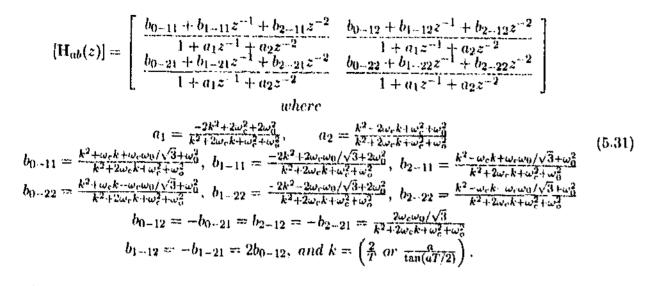

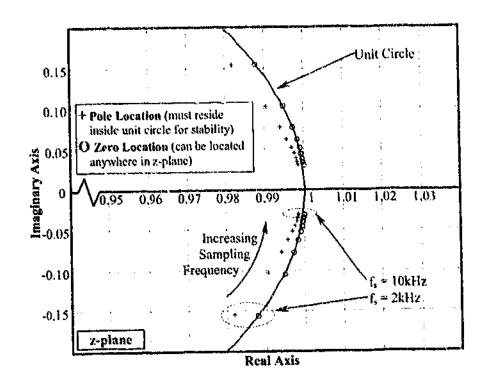

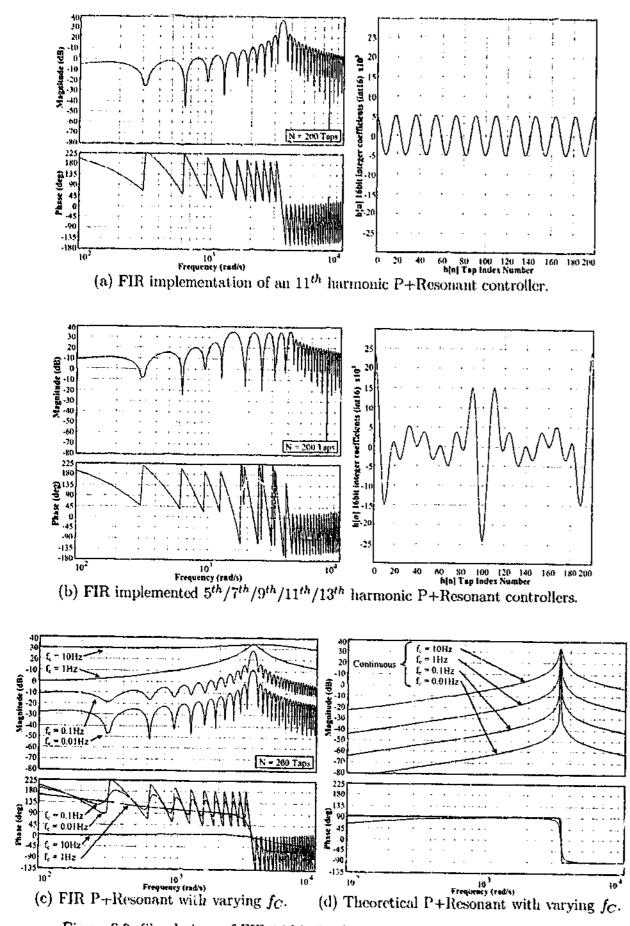

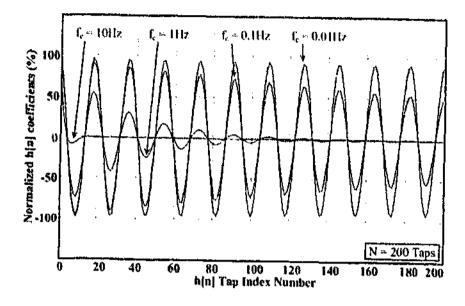

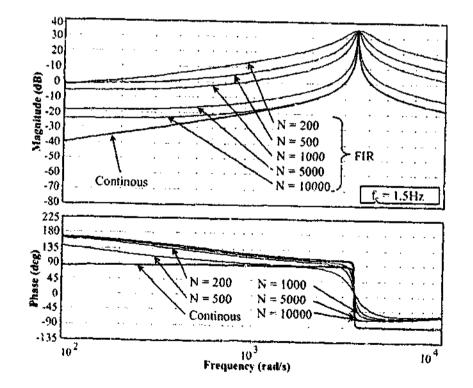

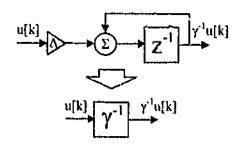

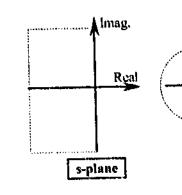

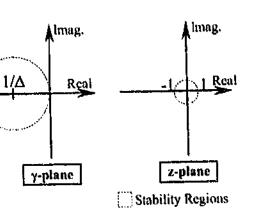

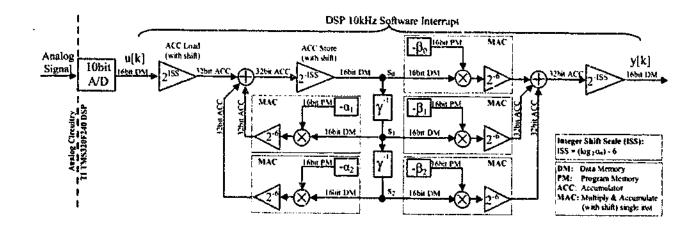

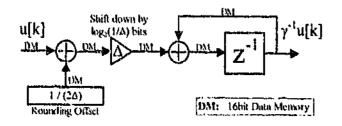

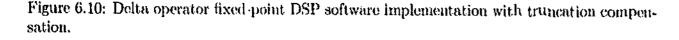

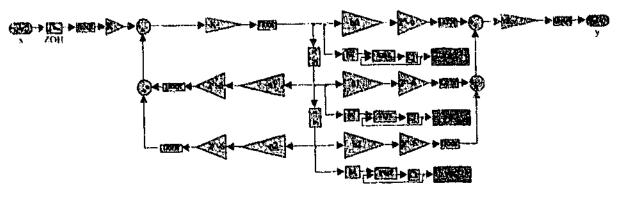

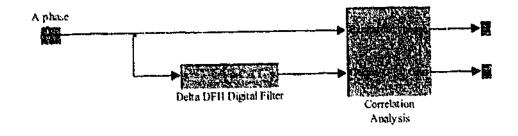

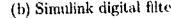

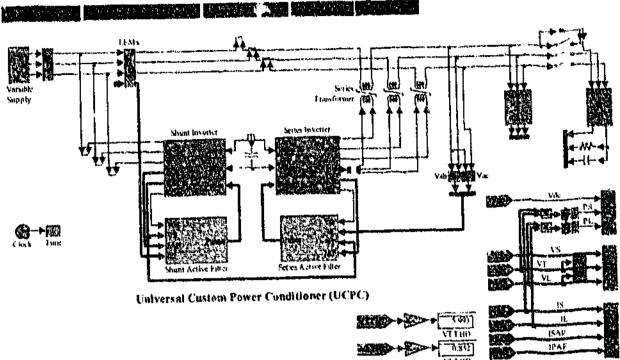

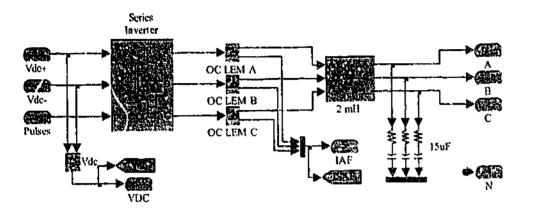

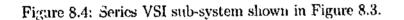

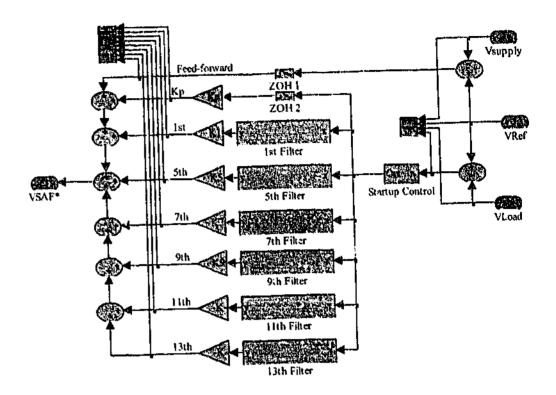

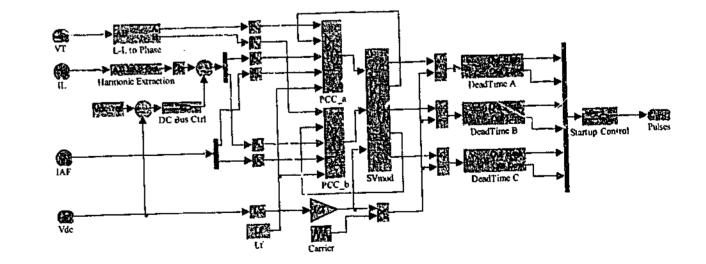

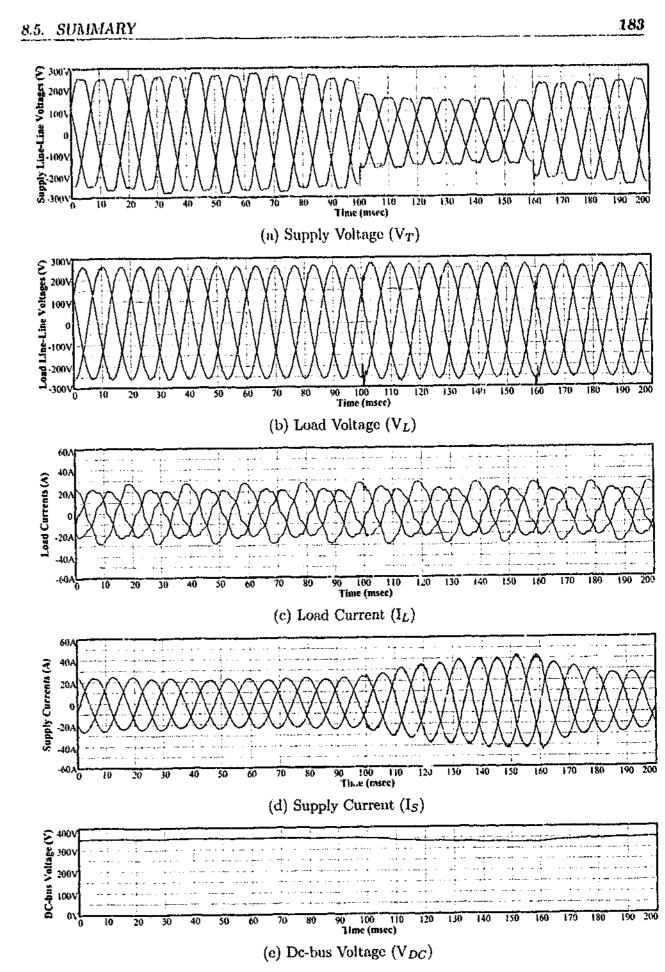

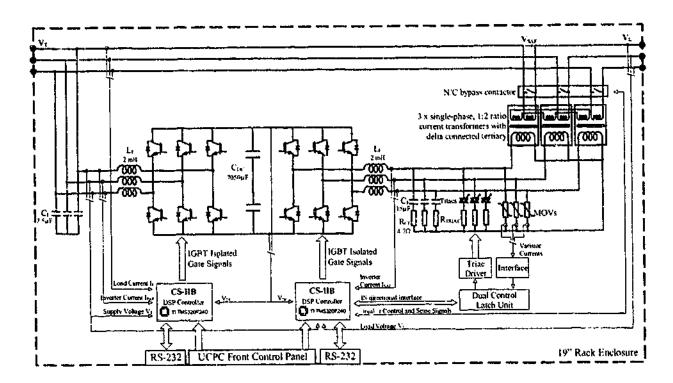

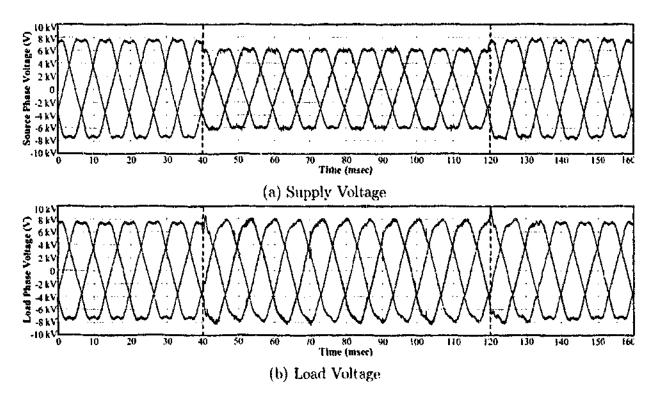

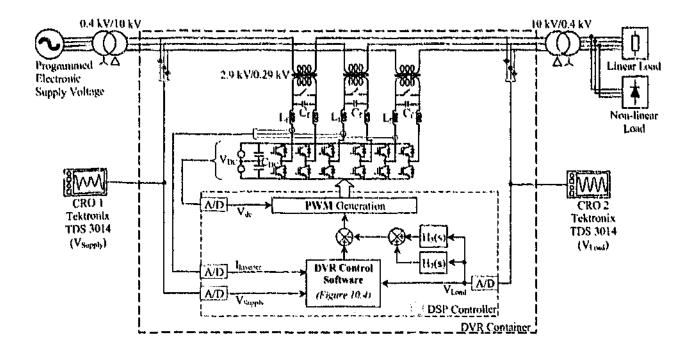

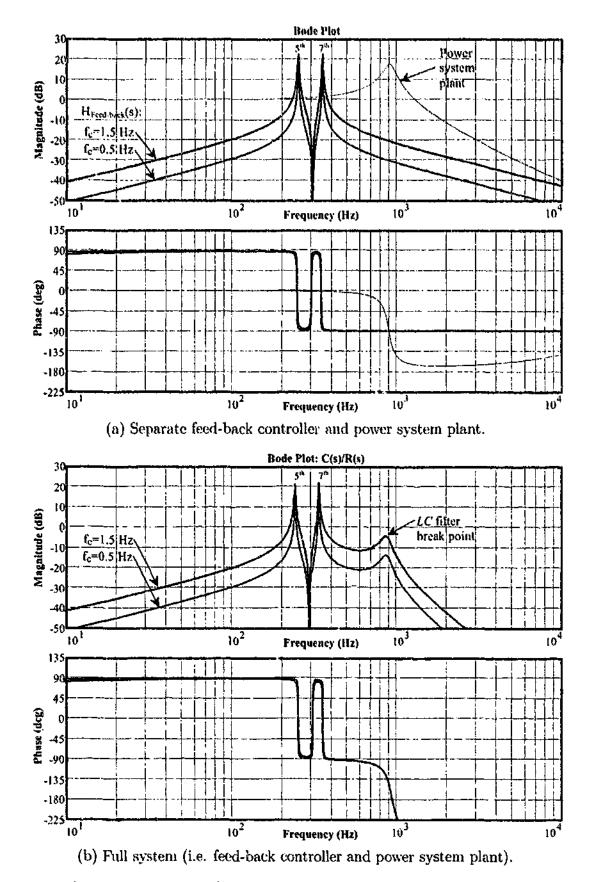

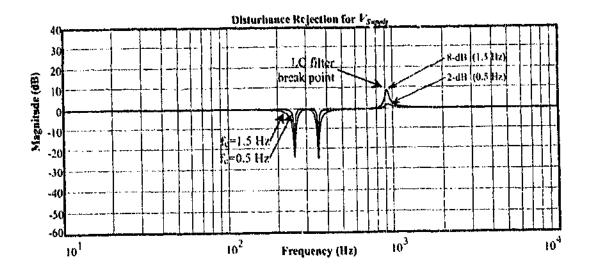

| $Y_a(s), Y_b(s)$               | a & b phase output variables ( <i>abc</i> reference frame)                        |